In this paper, the EMIF start-up mode of DM642 is mainly discussed from the aspects of software and hardware, combined with the DM642 development board that the author actually uses. All of these are personal understandings, which belong to the summary of students'time. If there are any inappropriate points, please criticize and correct them.

In the TI official document "TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor Data Manual" (SPRS 200), the "Bootmode" section describes the start-up mode of DM642. DM642 uses a low effective RESET signal. When the RESET signal is low, DM642 is reset and initialized to reset state. When the RESET signal is released, that is, the level is converted to high, the processor starts to run. DM642 has three startup modes: Host boot, EMIF boot and No boot. The actual DM642 development board uses the second startup mode, EMIF boot. Next, let's just introduce EMIFI boot. When the RESET signal is released and DM642 completes self-checking, it starts in EMIF boot mode and automatically copies the 1K-Bytes code of CE1 space starting to the starting address 0 through EDMA. During this process, the CPU stops and does not run. After the replication is completed, the CPU releases from the stop state and starts running from the zero address. It should be noted that the CE1 space starting 1K-Bytes data should be in the same format as the end format used by the system. We use the small-end format. In document SPRS200, it is written that After completion of the block transfer, the CPU is released from the "stalled" state and starts running from address 0. The word stalled is double quoted. I don't think the CPU really stops, but loads the second-level bootloader on the first-level bootloader, which is related to what we learn from books. After the CPU is released, the first-level bootloader is automatically run and EMIF and EDMA are configured to copy the CE1 address space starting 1K Bytes data to the starting address 0. But the size of 1K bytes is generally not enough to store the user's application. Therefore, the 1K byte starting from the CE1 address space stores the secondary bootloader, which loads the user's application program and data into RAM. To sum up, first of all, DM642 runs a bootloader after self-checking to complete the task of loading a bootloader. Next, the CPU jumps to address 0 and runs the second-level bootloader to load the user's program and data. Then jump to _c_init_and run. So far, the boot and loading of the system are completed.

The last paragraph tells us about it. DM642 Startup mode, which involves DM642 Address space, next DM642 Address space mapping. File SPRS200 In“ Memory Map Summary"Section pairs DM642 The address space is summarized. Here the emphasis is laid on the introduction. Internal memory(Internal RAM/L2,I used to call it L2),EMIFA Address space. L2 by DM642 On-chip integration Cache/SRAM Configurable memory, size 256 K-Bytes,Mapping address is 0 x0000 0000-0x0003 FFFF. L2 It is an important memory that is frequently used and related to program optimization. EMIFA The space is divided into four parts, respectively. CE0-3,Each space size is 256 MB,See the figure below for details.

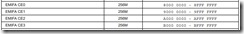

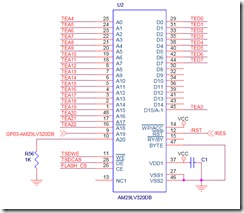

In the actual project, CE0 Address space configuration SDRAM,Size 32 M*64bit, Address range: 0 x8000 0000 – 0x81FF FFFF. The FLASH by AM29LV320D Asynchronous static memory, size 4 M*8bit,But in practice FLASH Work in Byte In mode, only 1 is mapped MBytes,because CE1 Address line only A[3-22]. Not in use FPGA/CPLD Under the conditions, make full use of FLASH Size 4 M*8bit Storage capacity, available DM642 Abundant GPIO To expand address space, implement FLASH Paging access, notably, is selected GPIO Must be satisfied DM642 Power up/Low level at reset. The following figure uses GPIO3 Implementing pairs FLASH Paging access, size 2 M*8bit,Configured in CE1D Address space: 0 x0000 0000 – 0x900F FFFF. The pin diagram is as follows

If you need to use it all FLASH 4 M*8bit Space, you can use more GPIO To achieve paging access, you only need to select GPIO In reposition/When power on, it is low level. In addition, it should be noted that software access is paging control.

In addition to the hardware start-up configuration, the software configuration also needs to be done.

1,Add Level 2 to your project bootloader(*.asm)Assembly code. (I use the IDE:CCSv5)

.title "Flash bootup utility for DM642 EVM" .option D,T .length 102 .width 140 COPY_TABLE .equ 0x90000400 EMIF_BASE .equ 0x01800000 .sect ".boot_load" .global _boot _boot: ;************************************************************************ ;* Debug Loop - Comment out B for Normal Operation ;************************************************************************ zero B1 _myloop: ; [!B1] B _myloop nop 5 _myloopend: nop ;************************************************************************ ;* Configure EMIF ;************************************************************************ mvkl emif_values, a3 ; load pointer to emif values mvkh emif_values, a3 mvkl EMIF_BASE, a4 ; load EMIF base address mvkh EMIF_BASE, a4 mvkl 0x0009, b0 ; load number of registers to set mvkh 0x0000, b0 emif_loop: ldw *a3++, b5 ; load register value sub b0,1,b0 ; decrement counter nop 2 [ b0] b emif_loop stw b5, *a4++ ; store register value nop 4 ;**************************************************************************** ;* Copy code sections ;**************************************************************************** mvkl COPY_TABLE, a3 ; load table pointer mvkh COPY_TABLE, a3 ldw *a3++, b1 ; Load entry point copy_section_top: ldw *a3++, b0 ; byte count ldw *a3++, a4 ; ram start address nop 3 [!b0] b copy_done ; have we copied all sections? nop 5 copy_loop: ldb *a3++,b5 sub b0,1,b0 ; decrement counter [ b0] b copy_loop ; setup branch if not done [!b0] b copy_section_top zero a1 [!b0] and 3,a3,a1 stb b5,*a4++ [!b0] and -4,a3,a5 ; round address up to next multiple of 4 [ a1] add 4,a5,a3 ; round address up to next multiple of 4 ;**************************************************************************** ;* Jump to entry point ;**************************************************************************** copy_done: b .S2 b1 nop 5 emif_values: .long 0x00052078 ; GBLCTL .long 0x73a28e01 ; CECTL1 (Flash/FPGA) .long 0xffffffd3 ; CECTL0 (SDRAM) .long 0x00000000 ; Reserved .long 0x22a28a22 ; CECTL2 .long 0x22a28a22 ; CECTL3 .long 0x57115000 ; SDCTL .long 0x0000081b ; SDTIM (refresh period) .long 0x001faf4d ; SDEXT2,DSP/BIOS Of MEM To configure.

As mentioned before, level two bootloader After loading, CPU It will run from address 0, so it will run at level 2. bootloader 1 assigned at the beginning of address 0 KB Address space, soon L2 First 1 KB Configuration boot District.

And in the cmd In the file, the code segment in 1 is allocated to BOOT In memory.

SECTIONS { .boot_load > BOOT/**/ }This article will simply combine with the actual situation. DM642 Of EMIF The startup mode is introduced. If there are any mistakes, please give more advice.

Reprinted at: https://www.cnblogs.com/xiangai10000/p/James Yang.html