Platform: Code Composer Studio 10.3.1

MSP430F5529 LaunchPad™ Development Kit

(MSP‑EXP430F5529LP)

Hard knowledge

Synchronization mode of USCI

SPI overview

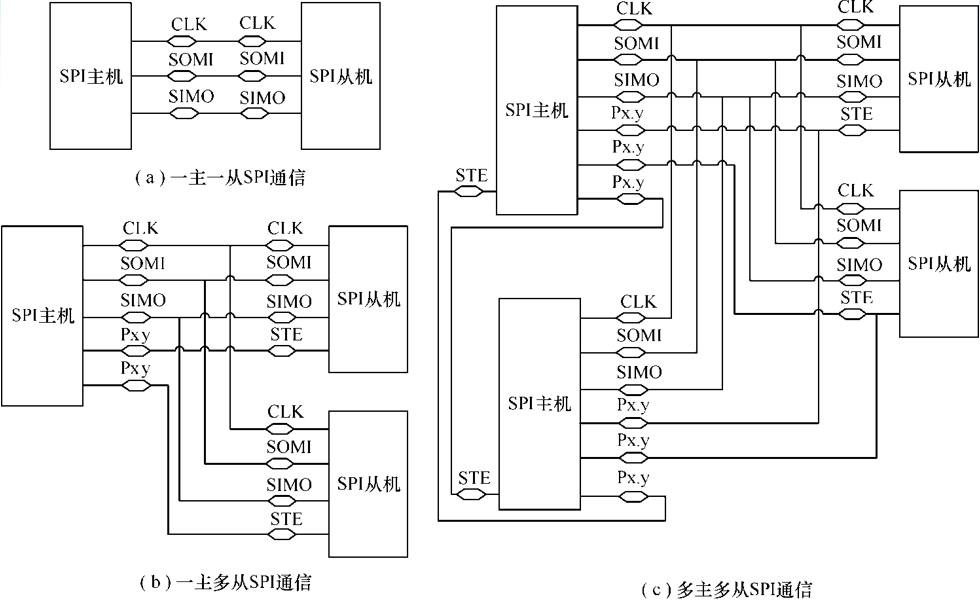

SPI (Serial Peripheral Interface) is the abbreviation of Serial Peripheral Interface. It is a synchronous full duplex communication protocol. Usci of MSP430F5xx/6xx Series MCU_ A and usci_ All B modules support SPI communication mode. SPI communication module communicates with the outside world through 3 wires (SOMI, SIMO, CLK) or 4 wires (SOMI, SIMO, CLK and STE). These four lines are briefly described below.

① CLK: CLK is SPI communication clock line. The clock line is controlled by the host, that is, the transmission rate is determined by the host programming.

② SOMI: SOMI (Slave Output Master Input) refers to the master input and slave output pins. If the device operates in host mode, this pin is input; If the device operates in slave mode, this pin is output.

③ SIMO: SIMO (Slave Input Master Output) is the Slave Input Master Output pin. If the device operates in host mode, this pin is output; If the device is operating in slave mode, this pin is the input.

④ STE: STE (Slave Transmit Enable) refers to the slave mode sending / receiving control pin, which controls multiple slaves in the multi master or multi slave system. In other applications, it is often written as Chip Select CS (Chip Select) and Slave Select SS (Slave Select).

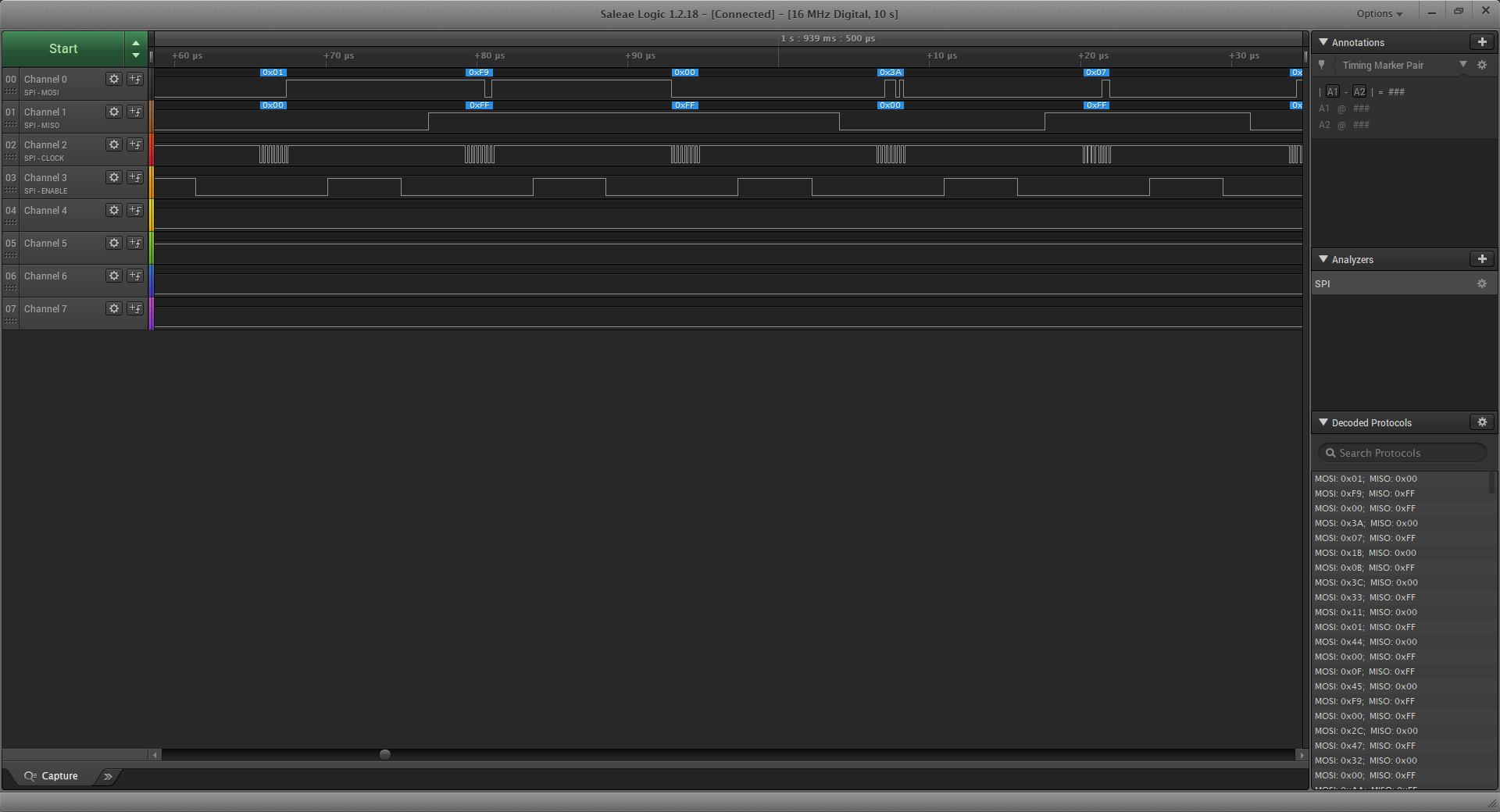

The hardware function of SPI communication module is very strong, which makes the implementation of SPI communication software quite simple, so that the CPU has more time to deal with other things. SPI communication principle is also relatively simple, as shown in the figure.

SPI characteristics and structure block diagram

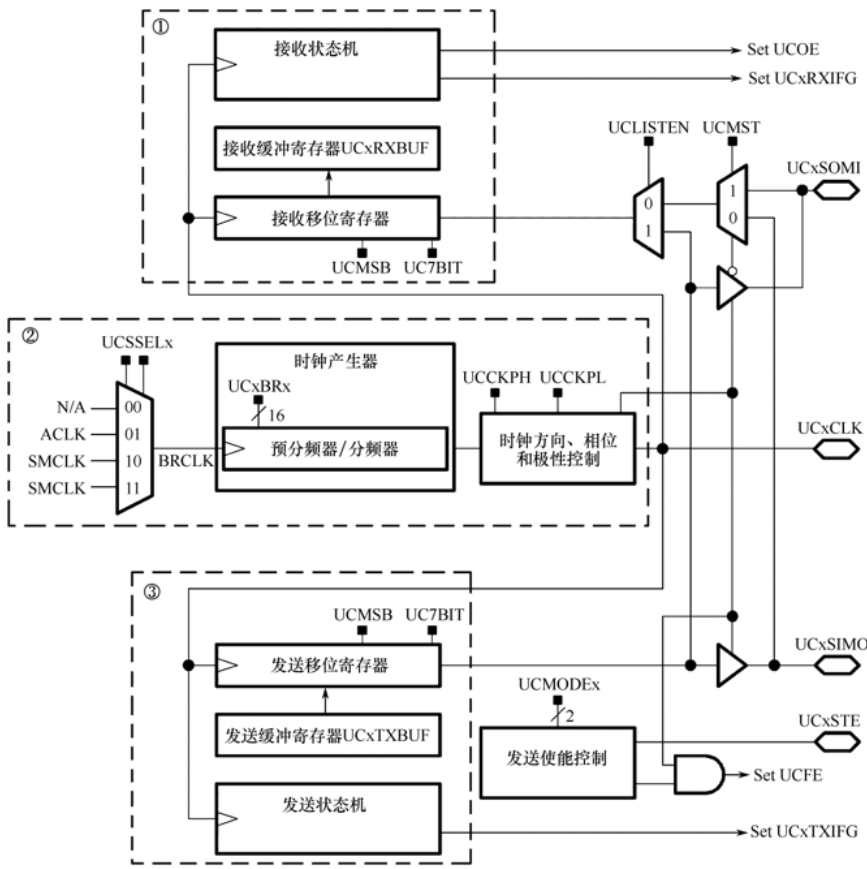

When the USCI module of MSP430 MCU controls the UCSYNC control position bit of the register UCAxCTL0 or UCBxCTL0, the USCI module works in the synchronous SPI mode. By configuring the UCMODEx control bit in the register, the SPI module can work in the three-wire or four wire SPI communication mode. The synchronous communication mode of MSP430 has the following characteristics:

7-bit or 8-bit data length;

data transmission and reception with the most significant bit first or the least significant bit first;

support 3-wire or 4-wire SPI operation;

support host mode or slave mode;

independent transmit and receive shift registers;

independent transmit and receive buffer registers;

continuous sending and receiving capability;

programmable clock polarity and phase;

in the main mode, the clock frequency is programmable;

independent receiving and sending interrupt capability;

slave mode operation under LPM4.

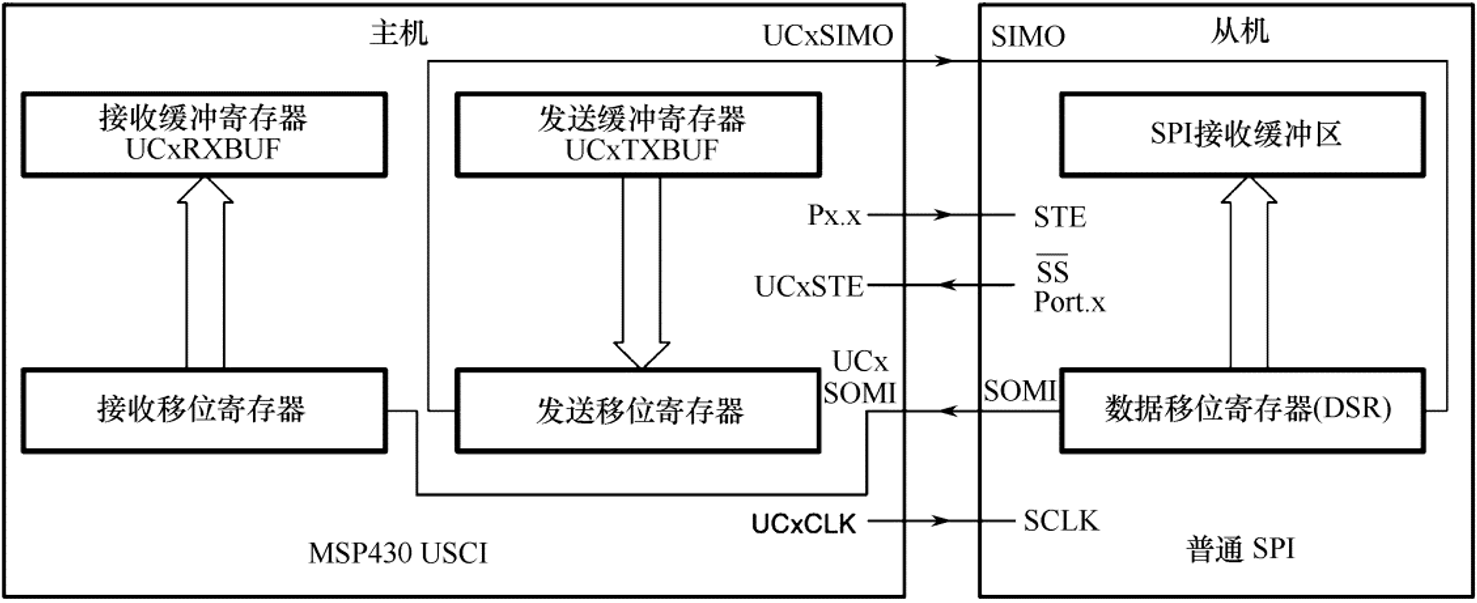

The USCI module is configured as the structure block diagram in SPI mode, as shown in the figure.

Synchronous operation principle and operation

(1) Host mode of SPI

When the USCI module of MSP430 MCU is used as SPI communication function, the connection diagram between the host and another SPI slave device with SPI interface is shown in the figure.

When ucmst in the control register UCAxCTL0/UCBxCTL0 = 1, the SPI communication module of MSP430 MCU works in the host mode. The USCI module controls serial communication through the clock signal on the UCxCLK pin. The serial communication transmission is completed by the transmission buffer UCxTXBUF, the transmission shift register and the UCxSIMO pin. When the shift register is empty, the data written into the transmission buffer will be moved into the transmission shift register and start the data transmission at UCxSIMO pin. Whether the data transmission is the most significant bit or the least significant bit first depends on the setting of UCMSB control bit. The serial communication receiving is completed by UCxSOMI pin, receiving shift register and receiving buffer UCxRXBUF. The data on the UCxSOMI pin is moved into the receive shift register at the clock edge opposite to the time of transmitting data. When all selected bits are received, the data in the receive shift register is moved into the receive buffer register UCxRXBUF and the receive interrupt flag bit UCRXIFG is set, indicating that the data reception / transmission has been completed.

(2) Slave mode of SPI

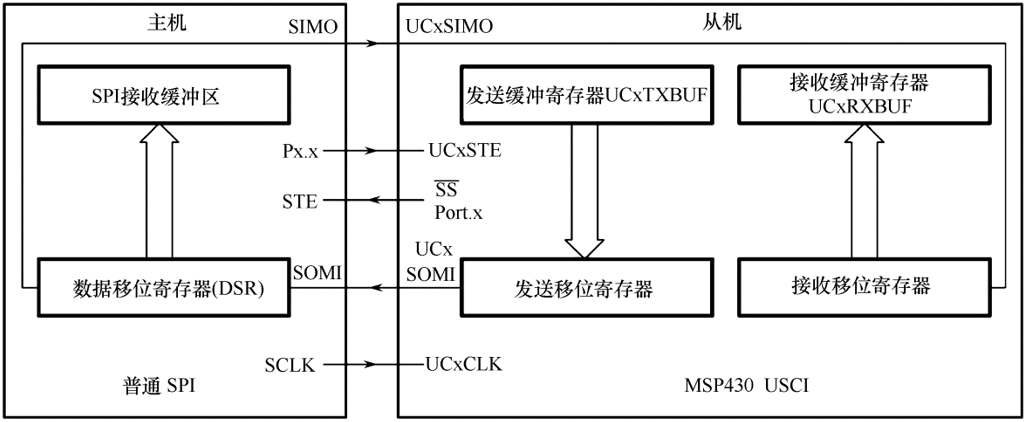

When the USCI module of MSP430 MCU is used as SPI communication function, the connection diagram between the slave and another SPI host device with SPI interface is shown in the figure.

When ucmst in the control register UCAxCTL0/UCBxCTL0 = 0, the SPI communication module of MSP430 MCU works in slave mode. In the slave mode, the serial clock used for SPI communication comes from the external host, and the UCxCLK pin of the slave is in the input state. The data transmission rate is determined by the serial clock sent by the host rather than the internal clock generator. Before the start of UCxCLK, the data moved into the shift register by UCxTXBUF is sent to the host through the UCxSOMI pin of the slave under the action of the host UCxCLK signal. At the same time, the serial data on the UCxSIMO pin is moved into the receive shift register in the reverse direction of the UCxCLK clock. When the data is moved from the receive shift register into the receive buffer register UCxRXBUF, the UCRXIFG interrupt flag position bit indicates that the data has been received. When the new data is written into the receive buffer register and the previous data has not been taken out, the overflow flag bit UCOE will be set.

(3) Serial clock control

The clock line UCxCLK required for serial communication is provided by the host on the SPI bus. When UCMST=1, the clock required for serial communication is provided by USCI clock generator. The reference clock used to generate serial communication clock is selected through UCSSELx control bit, and the final serial communication clock is output by UCxCLK pin. When UCMST=0, the USCI clock is provided by the UCxCLK pin of the host. At this time, USCI does not use the clock generator and does not consider the UCSSELx control bit. The receiver and transmitter of SPI operate in parallel, and the data transmission uses the same clock source.

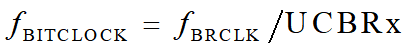

The value of 16 bit UCBRx composed of serial communication clock rate control registers (UCxxBR1 and UCxxBR0) is the frequency division factor of USCI clock source BRCLK. In the main mode, the maximum serial communication clock that USCI module can generate is BRCLK. The modulator cannot be used in SPI mode, that is, the SPI serial communication clock generator does not support fractional frequency division, so the calculation formula of the generation frequency of USCI clock generator working in SPI mode is

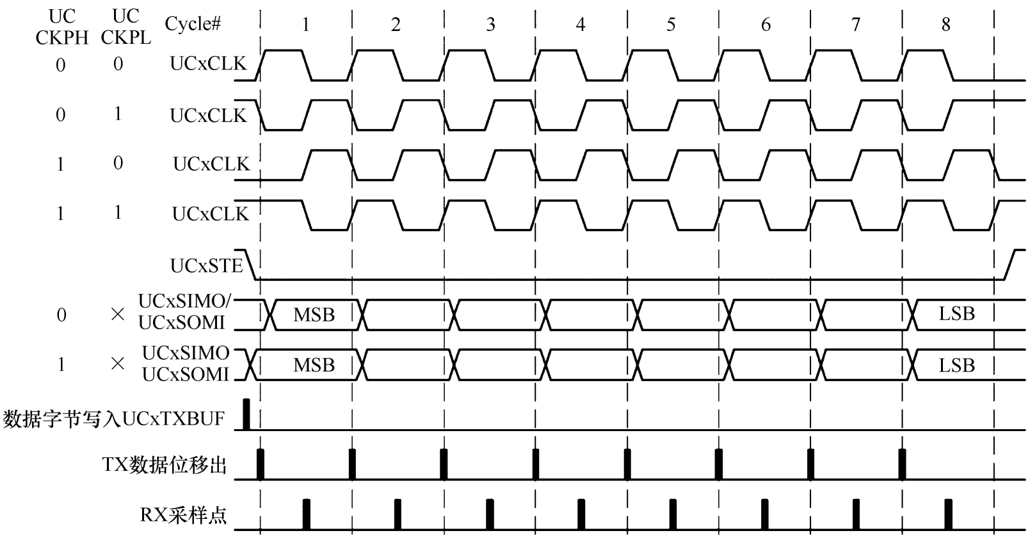

(4) SPI communication sequence diagram

SPI communication sequence diagram is shown in the figure. Among them, CKPH and CKPL are the polarity and phase control bits of UCxCLK. These two control bits are briefly introduced here. CKPH is the phase control bit of UCxCLK, and CKPL is the polarity control bit of UCxCLK. How to set the two control bits has no impact on the communication protocol, but is used to agree on the idle state of UCxCLK and where to start sampling signals. When CKPH=0, it means that the sampling signal starts at the first edge of UCxCLK, otherwise it starts at the second edge. When CKPL=0, it means that the clock bus is low-level idle, otherwise, it means that the clock bus is high-level idle. When the signal line is stable, receive sampling is carried out. When receiving sampling, the signal line is not allowed to have level jump.

(5) SPI interrupt

Usci module has only one interrupt vector, which is shared by sending and receiving. USCI_Ax and USCI_Bx does not share the same interrupt vector.

① SPI send interrupt operation

If UCTXIFG is set, it indicates that the transmission buffer register UCxTXBUF is empty and new characters can be written to it. If UCTXIE and GIE are also set, a send interrupt request will be generated. If characters are written into the UCxTXBUF buffer, the UCTXIFG will be reset automatically. Therefore, the transmission interrupt service program can be used to continuously write new data to the transmission buffer register UCxTXBUF to complete the data transmission. Note that when UCTXIFG=0, writing data to the UCxTXBUF buffer may cause incorrect data transmission.

② Receive interrupt SPI

Whenever a character is received and loaded into the receive buffer register UCxRXBUF, the receive interrupt flag bit UCRXIFG is set. If UCRXIE and GIE are also set, a receive interrupt request will be generated. When the receive buffer register UCxRXBUF is read, UCRXIFG will automatically reset. Therefore, the reception interrupt service program can be used to complete the reception of data.

③ USCI interrupt vector UCxIV

USCI interrupt flags have different priorities. Their combination shares one interrupt vector, that is, USCI is a multi-source interrupt. The interrupt vector register UCxIV is used to determine which interrupt flag requests to generate an interrupt. The interrupt with the highest priority will generate a digital offset in the UCxIV register, which will be accumulated to the program counter PC, and the program will automatically jump to the corresponding software program. Disabling interrupts does not affect the value of UCxIV. Any read or write access to the UCxIV register resets the interrupt flag with the highest pending priority. If another interrupt flag is set, another interrupt will be generated immediately after responding to the previous interrupt.

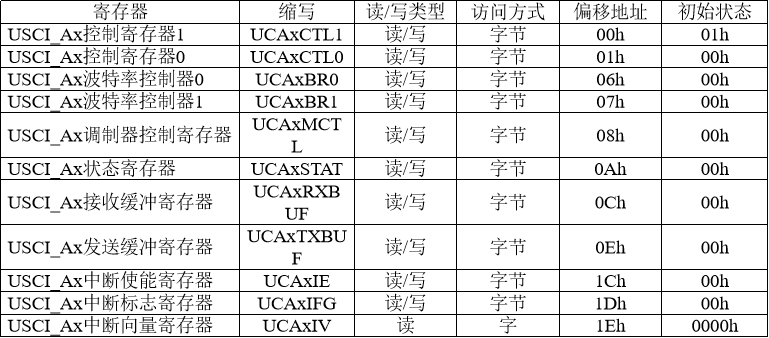

USCI register - SPI mode

The USCI registers available in SPI mode are shown in table. Due to USCI_Ax register and USCI_ The type and function of BX register are similar. Only USCI is listed here_ Ax register and explain the meaning of each of them. If user uses USCI_Bx module, refer to USCI_Ax registers are understood and configured.

USCI_x_SPI API (mechanical turnover)

To configure the module to host mode, the user must call USCI_x_SPI_initMaster() to configure USCI_x_SPI host mode. The next step is to use USCI_x_SPI_enable() enables USCI_x_SPI module. Then enable the interrupt if necessary. It is recommended to start usci before starting interrupt_ x_ SPI module. Then use USCI_x_SPI_transmitData() initializes data transmission, and then uses usci when setting the receive flag_ x_ SPI_ Receivedata() reads the received data, which indicates that the RX/TX operation has been completed.

To configure a module to slave mode, use USCI_x_SPI_initSlave()

Then use USCI_x_SPI_enable() enables the module. After that, the interrupt may

Enable when needed. When setting the receive flag, use usci first_ x_ SPI_ Transmitdata() transfers data and then uses USCI_x_SPI_receiveData() receives data.

USCI_x_SPI API is divided into 3 groups of functions:

Functions that handle state and initialization,

Functions that process data,

And functions to manage interrupts.

Functions that handle state and initialization

USCI_A_SPI_initMaster(uint16_t baseAddress, USCI_A_SPI_initMasterParam ∗param) //Initialize SPI host mode USCI_A_SPI_initSlave(uint16_t baseAddress, uint8_t msbFirst, uint8_t clockPhase, uint8_t clockPolarity) //Initialize SPI slave mode USCI_A_SPI_disable(uint16_t baseAddress) //Disable SPI module USCI_A_SPI_enable(uint16_t baseAddress) //Enable SPI module USCI_A_SPI_changeMasterClock(uint16_t baseAddress, USCI_A_SPI_changeMasterClockParam ∗param) //Initialize SPI master clock. At the end of this function call, the SPI module is left enabled USCI_A_SPI_isBusy(uint16_t baseAddress) //Indicates whether the SPI bus is busy

USCI_B_SPI_initMaster(uint16_t baseAddress, USCI_B_SPI_initMasterParam ∗param) //Initialize SPI host mode USCI_B_SPI_initSlave(uint16_t baseAddress, uint8_t msbFirst, uint8_t clockPhase, uint8_t clockPolarity) //Initialize SPI slave mode USCI_B_SPI_disable(uint16_t baseAddress) //Disable SPI module USCI_B_SPI_enable(uint16_t baseAddress) //Enable SPI module USCI_B_SPI_changeMasterClock(uint16_t baseAddress, USCI_B_SPI_changeMasterClockParam ∗param) //Initialize SPI master clock. At the end of this function call, the SPI module is left enabled USCI_B_SPI_isBusy(uint16_t baseAddress) //Indicates whether the SPI bus is busy

parameter

baseAddress

USCI_A0_BASE USCI_A1_BASE USCI_B0_BASE USCI_B1_BASE

USCI_A_SPI_initMasterParam

//*****************************************************************************

//

//! \brief Used in the USCI_A_SPI_initMaster() function as the param parameter.

//

//*****************************************************************************

typedef struct USCI_A_SPI_initMasterParam {

//! Selects Clock source.

//! \n Valid values are:

//! - \b USCI_A_SPI_CLOCKSOURCE_ACLK

//! - \b USCI_A_SPI_CLOCKSOURCE_SMCLK

uint8_t selectClockSource;

//! Is the frequency of the selected clock source

uint32_t clockSourceFrequency;

//! Is the desired clock rate for SPI communication

uint32_t desiredSpiClock;

//! Controls the direction of the receive and transmit shift register.

//! \n Valid values are:

//! - \b USCI_A_SPI_MSB_FIRST

//! - \b USCI_A_SPI_LSB_FIRST [Default]

uint8_t msbFirst;

//! Is clock phase select.

//! \n Valid values are:

//! - \b USCI_A_SPI_PHASE_DATA_CHANGED_ONFIRST_CAPTURED_ON_NEXT [Default]

//! - \b USCI_A_SPI_PHASE_DATA_CAPTURED_ONFIRST_CHANGED_ON_NEXT

uint8_t clockPhase;

//! \n Valid values are:

//! - \b USCI_A_SPI_CLOCKPOLARITY_INACTIVITY_HIGH

//! - \b USCI_A_SPI_CLOCKPOLARITY_INACTIVITY_LOW [Default]

uint8_t clockPolarity;

} USCI_A_SPI_initMasterParam;

USCI_B_SPI_initMasterParam

//*****************************************************************************

//

//! \brief Used in the USCI_B_SPI_initMaster() function as the param parameter.

//

//*****************************************************************************

typedef struct USCI_B_SPI_initMasterParam {

//! Selects Clock source.

//! \n Valid values are:

//! - \b USCI_B_SPI_CLOCKSOURCE_ACLK

//! - \b USCI_B_SPI_CLOCKSOURCE_SMCLK

uint8_t selectClockSource;

//! Is the frequency of the selected clock source

uint32_t clockSourceFrequency;

//! Is the desired clock rate for SPI communication

uint32_t desiredSpiClock;

//! Controls the direction of the receive and transmit shift register.

//! \n Valid values are:

//! - \b USCI_B_SPI_MSB_FIRST

//! - \b USCI_B_SPI_LSB_FIRST [Default]

uint8_t msbFirst;

//! Is clock phase select.

//! \n Valid values are:

//! - \b USCI_B_SPI_PHASE_DATA_CHANGED_ONFIRST_CAPTURED_ON_NEXT [Default]

//! - \b USCI_B_SPI_PHASE_DATA_CAPTURED_ONFIRST_CHANGED_ON_NEXT

uint8_t clockPhase;

//! \n Valid values are:

//! - \b USCI_B_SPI_CLOCKPOLARITY_INACTIVITY_HIGH

//! - \b USCI_B_SPI_CLOCKPOLARITY_INACTIVITY_LOW [Default]

uint8_t clockPolarity;

} USCI_B_SPI_initMasterParam;

msbFirst

//controls the direction of the receive and transmit shift register. Valid values are: USCI_A_SPI_MSB_FIRST USCI_A_SPI_LSB_FIRST //[Default]

clockPhase

//is clock phase select. Valid values are: USCI_A_SPI_PHASE_DATA_CHANGED_ONFIRST_CAPTURED_ON_NEXT //[Default] USCI_A_SPI_PHASE_DATA_CAPTURED_ONFIRST_CHANGED_ON_NEXT

clockPolarity

//Valid values are: USCI_A_SPI_CLOCKPOLARITY_INACTIVITY_HIGH USCI_A_SPI_CLOCKPOLARITY_INACTIVITY_LOW [Default]

USCI_A_SPI_changeMasterClockParam

//*****************************************************************************

//

//! \brief Used in the USCI_A_SPI_changeMasterClock() function as the param

//! parameter.

//

//*****************************************************************************

typedef struct USCI_A_SPI_changeMasterClockParam {

//! Is the frequency of the selected clock source

uint32_t clockSourceFrequency;

//! Is the desired clock rate for SPI communication

uint32_t desiredSpiClock;

} USCI_A_SPI_changeMasterClockParam;

USCI_B_SPI_changeMasterClockParam

//*****************************************************************************

//

//! \brief Used in the USCI_B_SPI_changeMasterClock() function as the param

//! parameter.

//

//*****************************************************************************

typedef struct USCI_B_SPI_changeMasterClockParam {

//! Is the frequency of the selected clock source

uint32_t clockSourceFrequency;

//! Is the desired clock rate for SPI communication

uint32_t desiredSpiClock;

} USCI_B_SPI_changeMasterClockParam;

Functions that process data

USCI_A_SPI_transmitData(uint16_t baseAddress, uint8_t transmitData) //Transfer a byte from SPI module USCI_A_SPI_receiveData(uint16_t baseAddress) //Receive bytes sent to SPI module

USCI_B_SPI_transmitData(uint16_t baseAddress, uint8_t transmitData) //Transfer a byte from SPI module USCI_B_SPI_receiveData(uint16_t baseAddress) //Receive bytes sent to SPI module

parameter

baseAddress

USCI_A0_BASE USCI_A1_BASE USCI_B0_BASE USCI_B1_BASE

transmitData

Data transmitted from SPI module

Functions to manage interrupts

USCI_A_SPI_disableInterrupt(uint16_t baseAddress, uint8_t mask) //Disable single SPI interrupt source USCI_A_SPI_enableInterrupt(uint16_t baseAddress, uint8_t mask) //Enable single SPl interrupt source USCI_A_SPI_getInterruptStatus(uint16_t baseAddress, uint8_t mask) //Gets the current SPI interrupt status USCI_A_SPI_clearInterrupt(uint16_t baseAddress, uint8_t mask) //Clear the selected SPl interrupt status flag

USCI_B_SPI_disableInterrupt(uint16_t baseAddress, uint8_t mask) //Disable single SPI interrupt source USCI_B_SPI_enableInterrupt(uint16_t baseAddress, uint8_t mask) //Enable single SPl interrupt source USCI_B_SPI_getInterruptStatus(uint16_t baseAddress, uint8_t mask) //Gets the current SPI interrupt status USCI_B_SPI_clearInterrupt(uint16_t baseAddress, uint8_t mask) //Clear the selected SPl interrupt status flag

parameter

baseAddress

USCI_A0_BASE USCI_A1_BASE USCI_B0_BASE USCI_B1_BASE

USCI_A_SPI's mask

/*is the bit mask of the interrupt sources to be disabled. Mask value is the logical OR of any of the following:*/ USCI_A_SPI_TRANSMIT_INTERRUPT USCI_A_SPI_RECEIVE_INTERRUPT

USCI_B_SPI's mask

/*is the bit mask of the interrupt sources to be disabled. Mask value is the logical OR of any of the following:*/ USCI_B_SPI_TRANSMIT_INTERRUPT USCI_B_SPI_RECEIVE_INTERRUPT

DMA related

USCI_A_SPI_getReceiveBufferAddressForDMA(uint16_t baseAddress) //Returns the address of RX buffer of SPI of DMA module USCI_A_SPI_getTransmitBufferAddressForDMA(uint16_t baseAddress) //Returns the address of TX buffer of SPI of DMA module

USCI_B_SPI_getReceiveBufferAddressForDMA(uint16_t baseAddress) //Returns the address of RX buffer of SPI of DMA module USCI_B_SPI_getTransmitBufferAddressForDMA(uint16_t baseAddress) //Returns the address of TX buffer of SPI of DMA module

parameter

baseAddress

USCI_A0_BASE USCI_A1_BASE USCI_B0_BASE USCI_B1_BASE

Actual combat

SPI driven ink screen

Introduction to ink screen

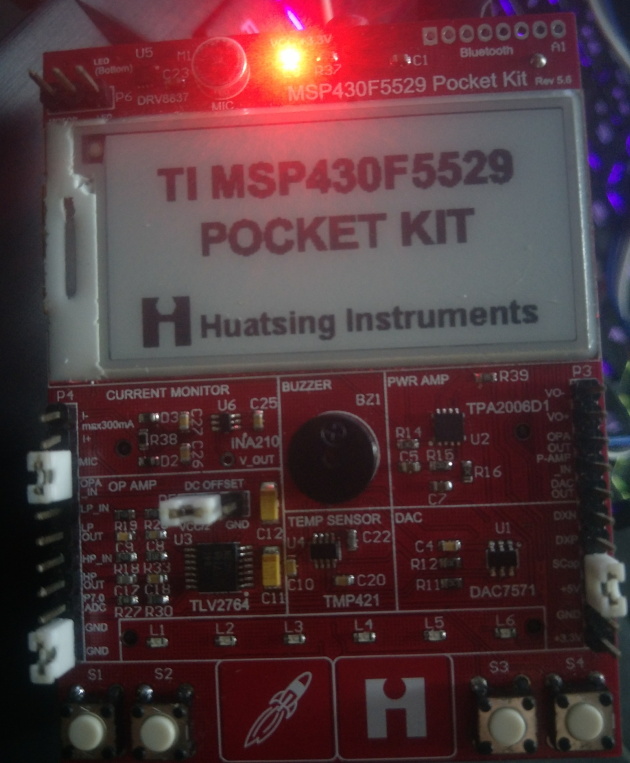

The F5529 pocket board does not use the common dot matrix LCD, Segment LCD, TFT and other screens, but uses electronic paper

(electronic ink screen) this innovative information display device is very different from the traditional display screen. It is briefly introduced below.

Classification of electronic paper

Like other display technologies, electronic paper is mainly divided into the following categories:

electrophoretic display technology (EPD): electrophoretic display technology encapsulates black and white charged particles in microcellular solution

In the drop structure, the rise and fall movement of black-and-white particles with different charges is controlled by an external electric field to show a monochromatic display

Show the effect. EPD technology is very suitable for black-and-white display with high reflectivity and high contrast

To make electronic paper, the electronic paper screen used on F5529 pocket board adopts this technology.

electronic powder fluid display technology (QR-LPD)

cholesterol liquid crystal display technology (CH LCD)

bistable nematic liquid crystal display technology (Bi TNLCD)

We haven't used these electronic paper technologies, so we won't introduce them here.

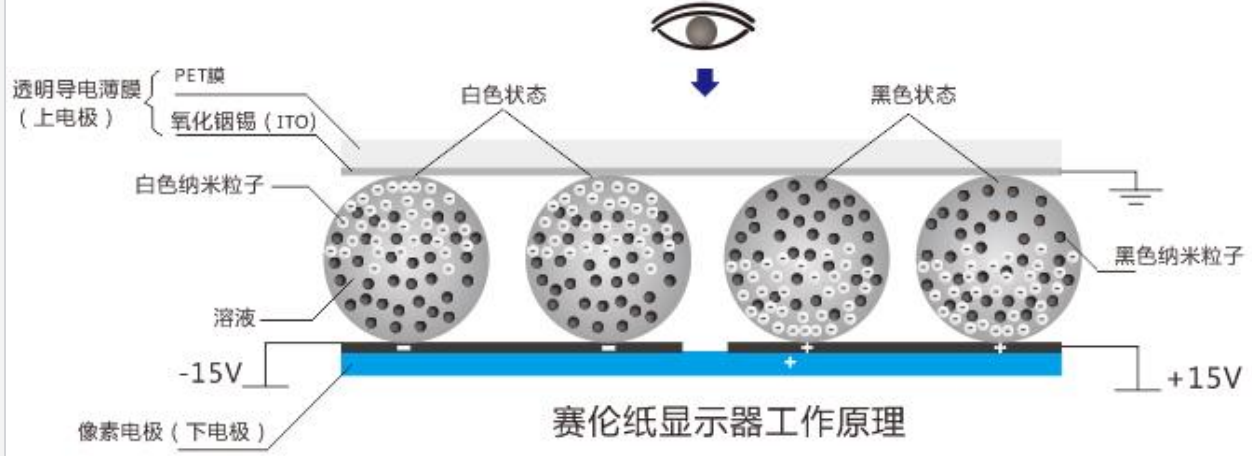

Detailed explanation of electrophoretic electronic paper technology

principle

Electrophoretic electronic paper technology (hereinafter referred to as electronic paper) is a "microcapsule electrophoretic display" technology. Its basic principle

It is the migration of charged nanoparticles suspended in liquid under the action of electric field. Electronic paper is a thin-film material

It is made by coating thousands of tiny capsule particles (called microcapsules) on a plastic substrate.

Microcapsule is the basic unit of electronic paper. It contains nanoparticles of two different colors.

structure

• electronic paper diaphragm: This is the core material of electronic paper display module, which is responsible for displaying the patterns actually seen by human eyes.

bottom plate: as the pixel electrode (lower electrode) of the electronic paper display screen, it is used to control the black and white color of each pixel of the electronic paper

Change. There are many types of backplane available, including PCB, FPC, TFT glass, PET, etc

Different soleplates can be selected according to specific needs. The electronic paper diaphragm can be laminated on the base plate.

• drive chip: corresponding logic level and timing can be generated according to control instructions and signals to control each backplane

The working sequence and state of pixels (or segment codes) and enables the electronic paper to display the required pattern.

• transparent protective film: a polymer plastic film with strong waterproof and vapor permeability. Compact it with a laminator

Attached to the electronic paper diaphragm and the base plate, it can effectively prevent water vapor from invading the Salem paper diaphragm and avoid the electronic paper from

Damaged by moisture.

edge sealing glue: a special chemical glue, which is evenly applied to the surrounding edges of the transparent protective film to isolate

The role of water vapor. It can prevent water vapor from penetrating into the transparent protective film and damaging the electronic paper diaphragm.

Advantages and disadvantages

As an innovative new method and equipment for information display, electronic paper is different from other display technologies in the following aspects

Several outstanding advantages:

readability:

Electronic paper displays patterns by reflecting ambient light. It has the effect of paper printing. And traditional transmission

Compared with liquid crystal display (TFT, etc.), it is still clear and visible even in strong sunlight; Visual angle

The degree is almost 180 °. In addition, the electronic paper display is soft and flicker free, so the "electronic paper books" are all powered by electricity

Make a screen out of sub paper.

super power saving:

Electronic paper only consumes power when refreshing the screen, and it can maintain the last time before power failure after power failure

The display of frame pictures is impossible for other screens. In addition, there is no need for backlight, so electronic paper is suitable for cooperation

Used for electronic labels.

thin and flexible:

Compared with other display screens, electronic paper has obvious advantages in thickness and weight, and is the thinnest

It can be 0.1mm, which is similar to the thickness of the paper. If the plastic film is used as the base material, it can also be bent

Characteristics of the song.

The above are the advantages of e-paper. Now let's talk about the current shortcomings of e-paper and these technical deficiencies

And the high cost will be gradually solved with the development of technology in the future.

slow refresh speed:

In particular, the refresh speed of electrophoretic electronic paper is relatively slow. At present, it is impossible to make animation or dynamic viewing

Frequency display.

poor color restoration:

At present, the color restoration of electronic paper is not as real and bright as TFT and other screens, so it can not be displayed well

For color photos and cost reasons, at present, electronic paper is mainly dot color gray scale.

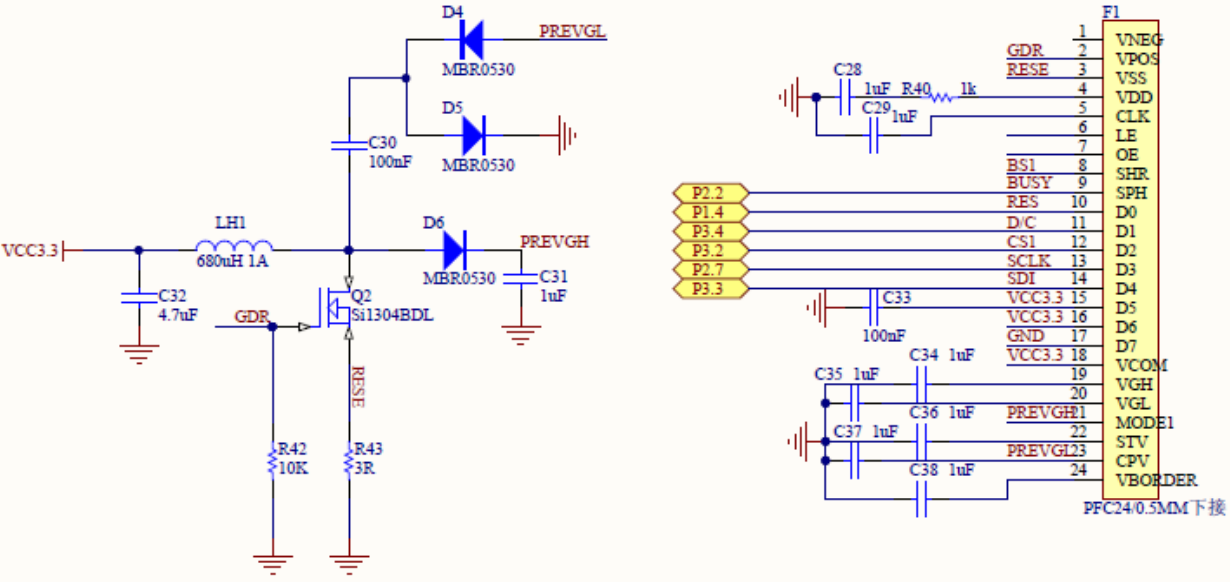

Introduction of experimental circuit

F5529 pocket board uses a piece with a resolution of 250 × 122 2.1-inch electronic paper, SPI interface.

Program analysis

Pin initialization

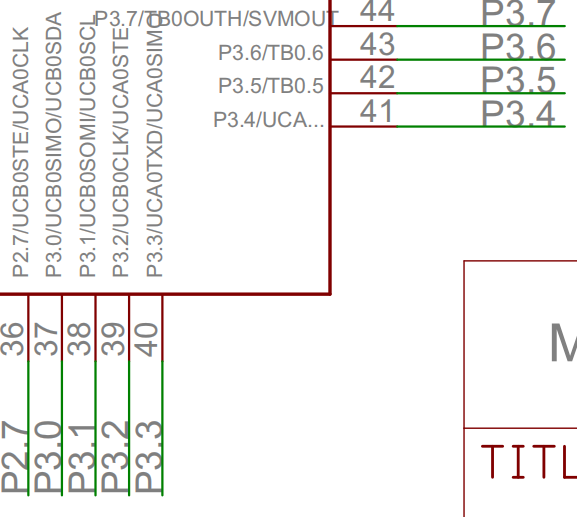

According to the schematic diagram, P3 4 is not used as SOMI pin, but is used to distinguish whether the signal type is control command or data, so only P2 7 multiplexed to CLK, P3 3 multiplexing is SIMO and others are set as GPIO

void PaperIO_Int(void)

{

//Set P1.4 for slave reset

GPIO_setAsOutputPin(GPIO_PORT_P1, GPIO_PIN4);

//Set P2.2 for BUSY

GPIO_setAsInputPin(GPIO_PORT_P2, GPIO_PIN2);

//Set P3.2 for CS

GPIO_setAsOutputPin(GPIO_PORT_P3, GPIO_PIN2);

//Set P3.4 for output mode

GPIO_setAsOutputPin(GPIO_PORT_P3, GPIO_PIN4);

//P2.7 option select (CLK)

GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_P2, GPIO_PIN7);

//P3.3 option select (SIMO)

GPIO_setAsPeripheralModuleFunctionInputPin(GPIO_PORT_P3, GPIO_PIN3);

nCS_H;

}

SPI module initialization

Set SPI clock source, SPI CLK to 5M, and enable interrupt

#define SPICLK 5000000

//Initialize Master

USCI_A_SPI_initMasterParam param = {0};

param.selectClockSource = USCI_A_SPI_CLOCKSOURCE_SMCLK;

param.clockSourceFrequency = UCS_getSMCLK();

param.desiredSpiClock = SPICLK;

param.msbFirst = USCI_A_SPI_MSB_FIRST;

param.clockPhase = USCI_A_SPI_PHASE_DATA_CHANGED_ONFIRST_CAPTURED_ON_NEXT;

param.clockPolarity = USCI_A_SPI_CLOCKPOLARITY_INACTIVITY_HIGH;

if (STATUS_FAIL == USCI_A_SPI_initMaster(USCI_A0_BASE, ¶m))

return;

//Enable SPI module

USCI_A_SPI_enable(USCI_A0_BASE);

//Enable Receive interrupt

USCI_A_SPI_clearInterrupt(USCI_A0_BASE, USCI_A_SPI_RECEIVE_INTERRUPT);

USCI_A_SPI_enableInterrupt(USCI_A0_BASE, USCI_A_SPI_RECEIVE_INTERRUPT);

__bis_SR_register(GIE);

Send and receive

Control command sending

void SPI4W_WRITECOM(unsigned char INIT_COM)

{

unsigned char TEMPCOM;

unsigned char scnt;

TEMPCOM=INIT_COM;

nCS_H;

nCS_L;

nDC_L;

//USCI_A0 TX buffer ready?

while (!USCI_A_SPI_getInterruptStatus(USCI_A0_BASE, USCI_A_SPI_TRANSMIT_INTERRUPT)) ;

//Transmit Data to slave

USCI_A_SPI_transmitData(USCI_A0_BASE, TEMPCOM);

while (!USCI_A_SPI_getInterruptStatus(USCI_A0_BASE, USCI_A_SPI_TRANSMIT_INTERRUPT)) ;

nCS_H;

}

Data transmission

void SPI4W_WRITEDATA(unsigned char INIT_DATA)

{

unsigned char TEMPCOM;

unsigned char scnt;

TEMPCOM=INIT_DATA;

nCS_H;

nCS_L;

nDC_H;

//USCI_A0 TX buffer ready?

while (!USCI_A_SPI_getInterruptStatus(USCI_A0_BASE, USCI_A_SPI_TRANSMIT_INTERRUPT)) ;

//Transmit Data to slave

USCI_A_SPI_transmitData(USCI_A0_BASE, TEMPCOM);

while (!USCI_A_SPI_getInterruptStatus(USCI_A0_BASE, USCI_A_SPI_TRANSMIT_INTERRUPT)) ;

nCS_H;

}

Interrupt service function

In this example, you do not need to receive data, but you need to enable the sending interrupt. The receiving function here is left for you to expand

//******************************************************************************

//

//This is the USCI_A0 interrupt vector service routine.

//

//******************************************************************************

uint8_t receiveData = 0x00;

#pragma vector=USCI_A0_VECTOR

__interrupt

void USCI_A0_ISR (void)

{

switch (__even_in_range(UCA0IV,4)){

//Vector 2 - RXIFG

case 2:

//USCI_A0 TX buffer ready?

while (!USCI_A_SPI_getInterruptStatus(USCI_A0_BASE, USCI_A_SPI_TRANSMIT_INTERRUPT));

receiveData = USCI_A_SPI_receiveData(USCI_A0_BASE);

break;

default: break;

}

}

All source code

main.c

#include "main.h"

#include "Paper_Display.h"

void SystemClock_Init(void)

{

PMM_setVCore(PMM_CORE_LEVEL_3); //High dominant frequency operation requires high core voltage

//XT1 pin multiplexing

GPIO_setAsPeripheralModuleFunctionInputPin(GPIO_PORT_P5, GPIO_PIN4);

GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_P5, GPIO_PIN5);

//Starting vibration XT1

UCS_turnOnLFXT1(UCS_XT1_DRIVE_3,UCS_XCAP_3);

//XT2 pin multiplexing

GPIO_setAsPeripheralModuleFunctionInputPin(GPIO_PORT_P5, GPIO_PIN2);

GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_P5, GPIO_PIN3);

//Starting vibration XT2

UCS_turnOnXT2(UCS_XT2_DRIVE_4MHZ_8MHZ);

//XT2 as FLL reference clock

UCS_initClockSignal(UCS_FLLREF, UCS_XT2CLK_SELECT, UCS_CLOCK_DIVIDER_8);

UCS_initFLLSettle(25000, 50);

//XT1 as ACLK clock source = 32768Hz

UCS_initClockSignal(UCS_ACLK, UCS_XT1CLK_SELECT, UCS_CLOCK_DIVIDER_1);

//DCOCLK as MCLK clock source

UCS_initClockSignal(UCS_MCLK, UCS_DCOCLK_SELECT, UCS_CLOCK_DIVIDER_1);

//DCOCLK as SMCLK clock source

UCS_initClockSignal(UCS_SMCLK, UCS_DCOCLK_SELECT, UCS_CLOCK_DIVIDER_1);

//Set the frequency of the external clock source so that when calling UCS_getMCLK, UCS_getSMCLK or UCS_ The correct value can be obtained when getaclk

UCS_setExternalClockSource(32768, 4000000);

}

#define SPICLK 5000000

int main(void)

{

WDT_A_hold(WDT_A_BASE);

SystemClock_Init();

PaperIO_Int();

//Initialize Master

USCI_A_SPI_initMasterParam param = {0};

param.selectClockSource = USCI_A_SPI_CLOCKSOURCE_SMCLK;

param.clockSourceFrequency = UCS_getSMCLK();

param.desiredSpiClock = SPICLK;

param.msbFirst = USCI_A_SPI_MSB_FIRST;

param.clockPhase = USCI_A_SPI_PHASE_DATA_CHANGED_ONFIRST_CAPTURED_ON_NEXT;

param.clockPolarity = USCI_A_SPI_CLOCKPOLARITY_INACTIVITY_HIGH;

if (STATUS_FAIL == USCI_A_SPI_initMaster(USCI_A0_BASE, ¶m))

return;

//Enable SPI module

USCI_A_SPI_enable(USCI_A0_BASE);

//Enable Receive interrupt

USCI_A_SPI_clearInterrupt(USCI_A0_BASE, USCI_A_SPI_RECEIVE_INTERRUPT);

USCI_A_SPI_enableInterrupt(USCI_A0_BASE, USCI_A_SPI_RECEIVE_INTERRUPT);

__bis_SR_register(GIE);

INIT_SSD1673();

Init_buff();

// display(" ", 42, 0,TimesNewRoman,size8,1,0);

// display(" Huatsing Instruments ", 42, 16,TimesNewRoman,size8,1,0);

// display("012abcABC",80, 0,TimesNewRoman,size16,0,0);

// display("012abcABC", 0,50,Arial,size8,1,0);

// display("012abcABC",80,50,Arial,size16,1,0);

// display("012abcABC", 0,90,ArialBlack,size8,1,0);

// display("012abcABC",80,90,ArialBlack,size16,1,0);

// DIS_IMG(1);

DIS_IMG(2);

// DIS_IMG(3);

while(1)

{

}

}

//******************************************************************************

//

//This is the USCI_A0 interrupt vector service routine.

//

//******************************************************************************

uint8_t receiveData = 0x00;

#pragma vector=USCI_A0_VECTOR

__interrupt

void USCI_A0_ISR (void)

{

switch (__even_in_range(UCA0IV,4)){

//Vector 2 - RXIFG

case 2:

//USCI_A0 TX buffer ready?

while (!USCI_A_SPI_getInterruptStatus(USCI_A0_BASE, USCI_A_SPI_TRANSMIT_INTERRUPT));

receiveData = USCI_A_SPI_receiveData(USCI_A0_BASE);

break;

default: break;

}

}

main.h

/* * main.h * * Created on: 2021 July 31 * Author: Royic */ #ifndef MAIN_H_ #define MAIN_H_ #include "driverlib.h" #define MCLK_IN_HZ 25000000 #define delay_us(x) __delay_cycles((MCLK_IN_HZ/1000000*(x))) #define delay_ms(x) __delay_cycles((MCLK_IN_HZ/1000*(x))) void SystemClock_Init(void); #endif /* MAIN_H_ */

Ink screen related

Paper_Display.c

#include "Include.h"

#include "Paper_Display.h"

#include "main.h"

#define DELAY_TIME / / dwell time (unit: 50 seconds)

// Test chart

#define PIC_ White 255 / / all white

#define PIC_ Black 254 / / all black

#define PIC_ Orientation 253 / / orientation

#define PIC_ LEFT_ BLACK_ RIGHT_ White 249 / / black left and white right

#define PIC_ UP_ BLACK_ DOWN_ White 248 / / black at the top and white at the bottom

const unsigned char init_data[]=

{

0x50,0xAA,0x55,0xAA,0x55,0xAA,0x11,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x0F,0x0F,0x0F,0x0F,

0x0F,0x0F,0x0F,0x01,0x00,0x00,0x00,0x00,0x00,

};

void MyRESET()

{

nRST_L;

delay_ms(10);

nRST_H;

delay_ms(10);

}

void DELAY_S(unsigned int delaytime) // 1s

{

unsigned int i;

for(i = 0; i < delaytime; ++i)

delay_ms(1000);

}

void DELAY_M(unsigned int delaytime) // 1M

{

unsigned int i;

for(i = 0; i < delaytime; i++)

DELAY_S(60);

}

void READBUSY()

{

while(1)

{

if(nBUSY == 0)

return;

else

DELAY_S(1);

}

}

void FIRST_PICTURE()

{

SPI4W_WRITECOM(0x21);

SPI4W_WRITEDATA(0x83);

SPI4W_WRITECOM(0x22);

SPI4W_WRITEDATA(0xC4);

}

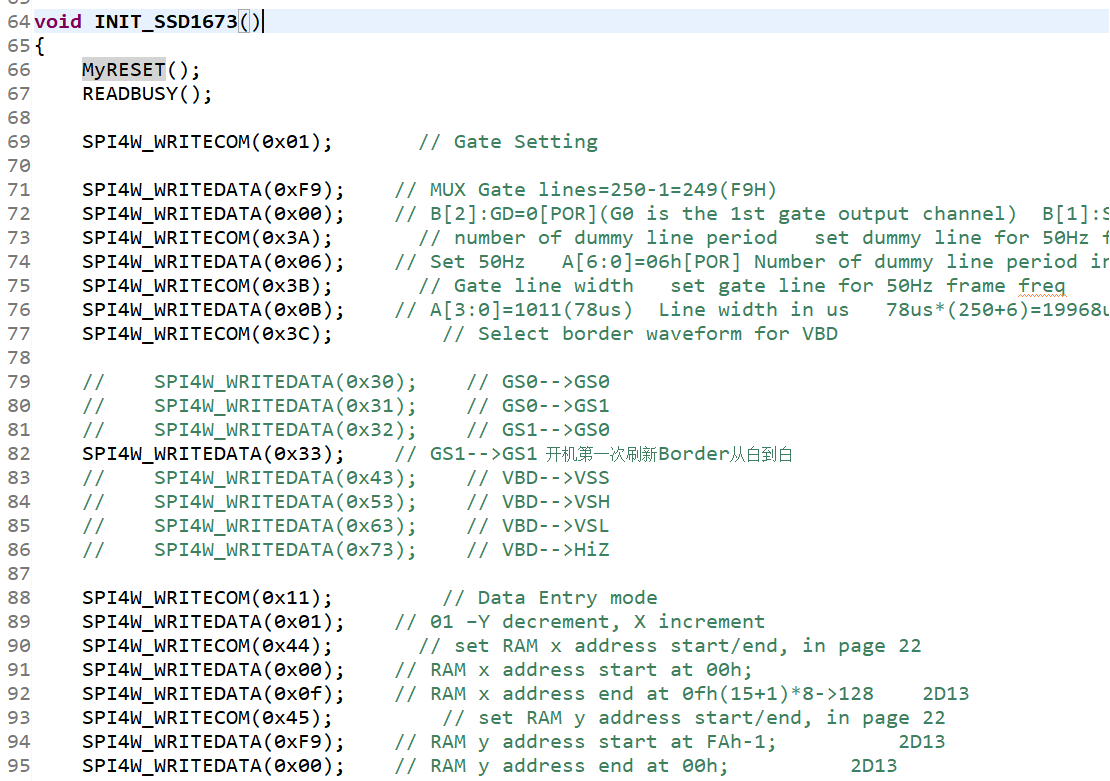

void INIT_SSD1673()

{

MyRESET();

READBUSY();

SPI4W_WRITECOM(0x01); // Gate Setting

SPI4W_WRITEDATA(0xF9); // MUX Gate lines=250-1=249(F9H)

SPI4W_WRITEDATA(0x00); // B[2]:GD=0[POR](G0 is the 1st gate output channel) B[1]:SM=0[POR](left and right gate interlaced) B[0]:TB=0[POR](scan from G0 to G319)

SPI4W_WRITECOM(0x3A); // number of dummy line period set dummy line for 50Hz frame freq

SPI4W_WRITEDATA(0x06); // Set 50Hz A[6:0]=06h[POR] Number of dummy line period in term of TGate

SPI4W_WRITECOM(0x3B); // Gate line width set gate line for 50Hz frame freq

SPI4W_WRITEDATA(0x0B); // A[3:0]=1011(78us) Line width in us 78us*(250+6)=19968us=19.968ms

SPI4W_WRITECOM(0x3C); // Select border waveform for VBD

// SPI4W_WRITEDATA(0x30); // GS0-->GS0

// SPI4W_WRITEDATA(0x31); // GS0-->GS1

// SPI4W_WRITEDATA(0x32); // GS1-->GS0

SPI4W_WRITEDATA(0x33); // GS1 -- > when GS1 is powered on, refresh the Border from white to white for the first time

// SPI4W_WRITEDATA(0x43); // VBD-->VSS

// SPI4W_WRITEDATA(0x53); // VBD-->VSH

// SPI4W_WRITEDATA(0x63); // VBD-->VSL

// SPI4W_WRITEDATA(0x73); // VBD-->HiZ

SPI4W_WRITECOM(0x11); // Data Entry mode

SPI4W_WRITEDATA(0x01); // 01 –Y decrement, X increment

SPI4W_WRITECOM(0x44); // set RAM x address start/end, in page 22

SPI4W_WRITEDATA(0x00); // RAM x address start at 00h;

SPI4W_WRITEDATA(0x0f); // RAM x address end at 0fh(15+1)*8->128 2D13

SPI4W_WRITECOM(0x45); // set RAM y address start/end, in page 22

SPI4W_WRITEDATA(0xF9); // RAM y address start at FAh-1; 2D13

SPI4W_WRITEDATA(0x00); // RAM y address end at 00h; 2D13

SPI4W_WRITECOM(0x2C); // Vcom= *(-0.02)+0.01???

// SPI4W_WRITEDATA(0x82); //-2.5V

// SPI4W_WRITEDATA(0x69); //-2V

SPI4W_WRITEDATA(0x4B); //-1.4V

// SPI4W_WRITEDATA(0x50); //-1.5V

// SPI4W_WRITEDATA(0x37); //-1V

// SPI4W_WRITEDATA(0x1E); //-0.5V

WRITE_LUT();

SPI4W_WRITECOM(0x21); // Option for Display Update

SPI4W_WRITEDATA(0x83); // A [7] = 1 (enable bypass) a [4] = 0 (value will be used as for bypass)

DIS_IMG(PIC_WHITE); // All black to all white screen, which can prevent the problem of flower screen when starting up

SPI4W_WRITECOM(0x21); //

SPI4W_WRITEDATA(0x03); // Compare the two pictures before and after the back refresh returns to normal

SPI4W_WRITECOM(0x3C); // Select border waveform for VBD

SPI4W_WRITEDATA(0x73); // When VBD -- > hiz is refreshed later, the Border is high impedance

}

void WRITE_LUT()

{

unsigned char i;

SPI4W_WRITECOM(0x32);//write LUT register

for(i=0;i<29;i++)

SPI4W_WRITEDATA(init_data[i]);//write LUT register

}

void Init_buff(void)

{

int i;

for(i=0;i<4000;i++)

{

DisBuffer[i]=gImage_logo[i];

}

}

//xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

//xx picture display function xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

//xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

void DIS_IMG(unsigned char num)

{

unsigned int row, col;

unsigned int pcnt;

SPI4W_WRITECOM(0x4E);

SPI4W_WRITEDATA(0x00); // set RAM x address count to 0;

SPI4W_WRITECOM(0x4F);

SPI4W_WRITEDATA(0xF9); // set RAM y address count to 250-1; 2D13

//DELAY_S(5);

delay_ms(5);

SPI4W_WRITECOM(0x24);

//DELAY_S(5);

delay_ms(5);

pcnt = 0; // Reset or save prompt byte sequence number

for(col=0; col<250; col++) // 250 GATE columns in total / / send 128x250bits ram 2D13

{

for(row=0; row<16; row++) // 128 SOURCE lines in total, 1 bit per pixel, i.e. 128 / 8 = 16 bytes

{

switch (num)

{

case 1:

SPI4W_WRITEDATA(DisBuffer[pcnt]);

break;

case 2:

SPI4W_WRITEDATA(gImage_logo[pcnt]);

break;

case PIC_WHITE:

SPI4W_WRITEDATA(0xff);

break;

default:

break;

}

pcnt++;

}

}

SPI4W_WRITECOM(0x22);

SPI4W_WRITEDATA(0xC7); // (Enable Clock Signal, Enable CP) (Display update,Disable CP,Disable Clock Signal)

// SPI4W_WRITEDATA(0xF7); // (Enable Clock Signal, Enable CP, Load Temperature value, Load LUT) (Display update,Disable CP,Disable Clock Signal)

SPI4W_WRITECOM(0x20);

delay_ms(1);

READBUSY();

//DELAY_S(DELAY_TIME);

delay_ms(50);

}

void SetpointXY(unsigned int xs,unsigned int xe,unsigned int ys,unsigned int ye)

{

SPI4W_WRITECOM(0x44);//set RAM x address start/end, in page 36

SPI4W_WRITEDATA(xs);//RAM x address start at 00h;

SPI4W_WRITEDATA(xe);//RAM x address end at 11h(17)->72: [because 1F(31)->128 and 12(18)->76]

SPI4W_WRITECOM(0x45);//set RAM y address start/end, in page 37

SPI4W_WRITEDATA(ys);//RAM y address start at 00h;

SPI4W_WRITEDATA(ye);//RAM y address start at ABh(171)->172: [because B3(179)->180]

SPI4W_WRITECOM(0x4E);//set RAM x address count to 0;

SPI4W_WRITEDATA(xs);

SPI4W_WRITECOM(0x4F);//set RAM y address count to 0;

SPI4W_WRITEDATA(ye);

SPI4W_WRITECOM(0x24);

}

void enterdeepsleep()

{

SPI4W_WRITECOM(0x10);

SPI4W_WRITEDATA(0x01);

}

void SPI4W_WRITECOM(unsigned char INIT_COM)

{

unsigned char TEMPCOM;

unsigned char scnt;

TEMPCOM=INIT_COM;

nCS_H;

nCS_L;

nDC_L;

//USCI_A0 TX buffer ready?

while (!USCI_A_SPI_getInterruptStatus(USCI_A0_BASE, USCI_A_SPI_TRANSMIT_INTERRUPT)) ;

//Transmit Data to slave

USCI_A_SPI_transmitData(USCI_A0_BASE, TEMPCOM);

while (!USCI_A_SPI_getInterruptStatus(USCI_A0_BASE, USCI_A_SPI_TRANSMIT_INTERRUPT)) ;

nCS_H;

}

void SPI4W_WRITEDATA(unsigned char INIT_DATA)

{

unsigned char TEMPCOM;

unsigned char scnt;

TEMPCOM=INIT_DATA;

nCS_H;

nCS_L;

nDC_H;

//USCI_A0 TX buffer ready?

while (!USCI_A_SPI_getInterruptStatus(USCI_A0_BASE, USCI_A_SPI_TRANSMIT_INTERRUPT)) ;

//Transmit Data to slave

USCI_A_SPI_transmitData(USCI_A0_BASE, TEMPCOM);

while (!USCI_A_SPI_getInterruptStatus(USCI_A0_BASE, USCI_A_SPI_TRANSMIT_INTERRUPT)) ;

nCS_H;

}

unsigned char FontSize[]={16,32};

void display(unsigned char *str, //character string

unsigned int xsize, //x-direction position

unsigned int ysize, //y-direction position

unsigned int font, //Font 0,1,2

unsigned int size, //Font size 0,1

unsigned int reverse,//Reverse display: 0 is displayed normally and 1 is displayed reversely

unsigned int fresh //Refresh now

)

{

unsigned char i,j,k;

unsigned char *zimoPoint;

unsigned char zimoW;

unsigned char zimoH;

unsigned char moveBytes; //Bytes moved

unsigned char moveBits; //Moving bits

volatile unsigned char zimoBufferTemp[6];

zimoW=FontSize[size]/2; //Number of rows in x direction

zimoH=FontSize[size]/8; //Bytes in y direction

moveBits=ysize%8;

if((moveBits)!=0) //Incomplete byte processing

{

moveBytes=zimoH+1;

}

else moveBytes=zimoH;

while(*str)

{

if((font==TimesNewRoman) && (size==size8)) zimoPoint=(unsigned char *)&TimesNewRoman8;

else if((font==TimesNewRoman) && (size==size16)) zimoPoint=(unsigned char *)&TimesNewRoman16;

zimoPoint=zimoPoint+((*str)-0x20)*zimoW*zimoH; //Point to the start address of the character font.

for(i=0;i<zimoW;i++)

{

//Read a column of data from the font

for(j=0;j<6;j++) zimoBufferTemp[j]=0;

if(reverse==0)

{

for(j=0;j<zimoH;j++)

{

zimoBufferTemp[j]=~(*(zimoPoint+i+j*zimoW));

}

}

else

{

for(j=0;j<zimoH;j++)

{

zimoBufferTemp[j]=(*(zimoPoint+i+j*zimoW));

}

}

//Font column data shift operation

if (moveBits==0);

else

{

for(k=0;k<moveBits;k++)

{

for(j=moveBytes;j>0;j--)

{

zimoBufferTemp[j]=zimoBufferTemp[j]>>1;

if ((zimoBufferTemp[j-1]&0x01)>0) zimoBufferTemp[j]=zimoBufferTemp[j]+0x80;

}

zimoBufferTemp[0]=zimoBufferTemp[0]>>1;

}

}

//Dispuffer processing

if (moveBits==0);

else

{

k=(0xff>>moveBits);

zimoBufferTemp[moveBytes-1]=zimoBufferTemp[moveBytes-1] | (DisBuffer[(xsize+i)*16+((ysize/8)+zimoH)] & k);

k=~k;

zimoBufferTemp[0]=zimoBufferTemp[0] | (DisBuffer[(xsize+i)*16+(ysize/8)] & k);

}

//Update dispuffer

for(j=0;j<moveBytes;j++)

{

DisBuffer[(xsize+i)*16+((ysize/8)+j)]=zimoBufferTemp[j];

}

}

xsize=xsize+zimoW;

str++;

}

}

void PaperIO_Int(void)

{

//Set P1.4 for slave reset

GPIO_setAsOutputPin(GPIO_PORT_P1, GPIO_PIN4);

//Set P2.2 for BUSY

GPIO_setAsInputPin(GPIO_PORT_P2, GPIO_PIN2);

//Set P3.2 for CS

GPIO_setAsOutputPin(GPIO_PORT_P3, GPIO_PIN2);

//Set P3.4 for output mode

GPIO_setAsOutputPin(GPIO_PORT_P3, GPIO_PIN4);

//P2.7 option select (CLK)

GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_P2, GPIO_PIN7);

//P3.3 option select (SIMO)

GPIO_setAsPeripheralModuleFunctionInputPin(GPIO_PORT_P3, GPIO_PIN3);

nCS_H;

}

Paper_Display.h

#include "main.h"

#define TimesNewRoman 0

#define Arial 1

#define ArialBlack 2

#define size8 0

#define size16 1

#define nRST_H GPIO_setOutputHighOnPin(GPIO_PORT_P1, GPIO_PIN4)

#define nRST_L GPIO_setOutputLowOnPin(GPIO_PORT_P1, GPIO_PIN4)

#define nCS_H GPIO_setOutputHighOnPin(GPIO_PORT_P3, GPIO_PIN2)

#define nCS_L GPIO_setOutputLowOnPin(GPIO_PORT_P3, GPIO_PIN2)

#define nDC_H GPIO_setOutputHighOnPin(GPIO_PORT_P3, GPIO_PIN4)

#define nDC_L GPIO_setOutputLowOnPin(GPIO_PORT_P3, GPIO_PIN4)

#define nBUSY GPIO_getInputPinValue(GPIO_PORT_P2, GPIO_PIN2)

extern volatile unsigned char DisBuffer[250*16];

void SPI4W_WRITECOM(unsigned char INIT_COM);

void SPI4W_WRITEDATA(unsigned char INIT_DATA);

void SPI4W_WRITE(unsigned char INIT_COM,unsigned char INIT_DATA);

void MYRESET(void);

void WRITE_LUT(void);

void INIT_SSD1673(void);

void DIS_IMG(unsigned char num);

void FIRST_PICTURE(void);

void IMAGE_WRITE(unsigned char patt_num);

void DELAY_S(unsigned int delaytime);

void DELAY_M(unsigned int delaytime);

void RING(void);

void READBUSY(void);

void closebump(void);

void DisplayString(const char* str, unsigned int sx, unsigned int sy);

void enterdeepsleep(void);

void Init_buff(void);

void SET_EYEONE(void);

void PaperIO_Int(void);

void display(unsigned char *str, //character string

unsigned int xsize, //x-direction position

unsigned int ysize, //y-direction position

unsigned int font, //Font 0,1,2

unsigned int size, //Font size 0,1

unsigned int reverse,//Reverse display: 0 is displayed normally and 1 is displayed reversely

unsigned int fresh //Refresh now

);

Include.h

/*

* Include.h

*

* Created on: 2013-11-12

* Author: Lenovo

*/

#ifndef INCLUDE_H_

#define INCLUDE_H_

#include <string.h>

#endif /* INCLUDE_H_ */

#define uchar unsigned char

#define uint unsigned int

#define TimesNewRoman 0

#define Arial 1

#define ArialBlack 2

#define size8 0

#define size16 1

volatile unsigned char DisBuffer[250*16];

const unsigned char TimesNewRoman8[]=

{

/* */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* ! */

0x00,0x00,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0xE8,0x00,0x00,0x00,0x00,0x00,

/* " */

0x00,0x1E,0x00,0x1E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* # */

0x02,0x02,0x07,0x3A,0x02,0x07,0x3A,0x02,0x40,0x78,0xC0,0x40,0x78,0xC0,0x40,0x40,

/* $ */

0x00,0x0E,0x11,0x3F,0x10,0x0C,0x00,0x00,0x00,0x30,0x08,0xFC,0x88,0x70,0x00,0x00,

/* % */

0x0E,0x11,0x11,0x0E,0x00,0x00,0x01,0x06,0x00,0x00,0x08,0x30,0x40,0x80,0x00,0x00,

/* & */

0x00,0x00,0x00,0x00,0x0F,0x11,0x12,0x1C,0x00,0x70,0x98,0x88,0x08,0xC8,0x30,0x28,

/* ' */

0x00,0x1E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* ( */

0x00,0x03,0x0C,0x10,0x20,0x00,0x00,0x00,0x00,0xF0,0x0C,0x02,0x01,0x00,0x00,0x00,

/* ) */

0x20,0x10,0x0C,0x03,0x00,0x00,0x00,0x00,0x01,0x02,0x0C,0xF0,0x00,0x00,0x00,0x00,

/* * */

0x00,0x12,0x0C,0x3F,0x0C,0x12,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* + */

0x01,0x01,0x01,0x0F,0x01,0x01,0x01,0x00,0x00,0x00,0x00,0xE0,0x00,0x00,0x00,0x00,

/* , */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x0A,0x0C,0x00,0x00,0x00,0x00,0x00,0x00,

/* - */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x40,0x40,0x40,0x00,0x00,0x00,0x00,

/* . */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x08,0x00,0x00,0x00,0x00,0x00,0x00,

/* / */

0x00,0x01,0x0E,0x30,0x00,0x00,0x00,0x00,0x18,0xE0,0x00,0x00,0x00,0x00,0x00,0x00,

/* 0 */

0x00,0x0F,0x10,0x10,0x10,0x0F,0x00,0x00,0x00,0xF0,0x08,0x08,0x08,0xF0,0x00,0x00,

/* 1 */

0x00,0x00,0x08,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x08,0xF8,0x08,0x00,0x00,0x00,

/* 2 */

0x00,0x08,0x10,0x10,0x11,0x0E,0x00,0x00,0x00,0x18,0x28,0x48,0x88,0x18,0x00,0x00,

/* 3 */

0x00,0x08,0x10,0x11,0x13,0x0C,0x00,0x00,0x00,0x08,0x08,0x08,0x08,0xF0,0x00,0x00,

/* 4 */

0x00,0x01,0x06,0x08,0x1F,0x00,0x00,0x00,0xC0,0x40,0x40,0x40,0xF8,0x40,0x00,0x00,

/* 5 */

0x00,0x02,0x0E,0x12,0x11,0x10,0x00,0x00,0x00,0x08,0x08,0x08,0x10,0xE0,0x00,0x00,

/* 6 */

0x00,0x03,0x05,0x0A,0x12,0x11,0x00,0x00,0x00,0xF0,0x08,0x08,0x08,0xF0,0x00,0x00,

/* 7 */

0x08,0x10,0x10,0x10,0x10,0x17,0x18,0x00,0x00,0x00,0x00,0x18,0xE0,0x00,0x00,0x00,

/* 8 */

0x00,0x0C,0x12,0x11,0x12,0x0C,0x00,0x00,0x00,0x70,0x88,0x08,0x88,0x70,0x00,0x00,

/* 9 */

0x00,0x0F,0x10,0x10,0x10,0x0F,0x00,0x00,0x00,0x08,0x88,0x90,0xA0,0xC0,0x00,0x00,

/* : */

0x00,0x02,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x08,0x00,0x00,0x00,0x00,0x00,0x00,

/* ; */

0x00,0x02,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x0A,0x0C,0x00,0x00,0x00,0x00,0x00,

/* < */

0x00,0x01,0x02,0x02,0x04,0x04,0x08,0x00,0x00,0x00,0x80,0x80,0x40,0x40,0x20,0x00,

/* = */

0x02,0x02,0x02,0x02,0x02,0x02,0x02,0x02,0x40,0x40,0x40,0x40,0x40,0x40,0x40,0x40,

/* > */

0x00,0x08,0x04,0x04,0x02,0x02,0x01,0x00,0x00,0x20,0x40,0x40,0x80,0x80,0x00,0x00,

/* ? */

0x00,0x0C,0x10,0x10,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0xE8,0x00,0x00,0x00,0x00,

/* @ */

0x00,0x03,0x04,0x08,0x11,0x22,0x24,0x24,0x00,0xF8,0x04,0x02,0xF1,0x08,0x08,0x10,

/* A */

0x00,0x00,0x00,0x01,0x06,0x18,0x06,0x01,0x08,0x08,0x38,0xC8,0x40,0x40,0x40,0xC8,

/* B */

0x00,0x10,0x1F,0x11,0x11,0x11,0x11,0x0E,0x00,0x08,0xF8,0x08,0x08,0x08,0x08,0x90,

/* C */

0x00,0x07,0x08,0x10,0x10,0x10,0x10,0x08,0x00,0xE0,0x10,0x08,0x08,0x08,0x08,0x10,

/* D */

0x00,0x10,0x1F,0x10,0x10,0x10,0x10,0x08,0x00,0x08,0xF8,0x08,0x08,0x08,0x08,0x10,

/* E */

0x00,0x10,0x1F,0x11,0x11,0x13,0x10,0x18,0x00,0x08,0xF8,0x08,0x08,0x88,0x08,0x18,

/* F */

0x00,0x10,0x1F,0x11,0x11,0x13,0x10,0x18,0x00,0x08,0xF8,0x08,0x00,0x80,0x00,0x00,

/* G */

0x00,0x07,0x08,0x10,0x10,0x10,0x10,0x08,0x00,0xE0,0x10,0x08,0x08,0x08,0x08,0x88,

/* H */

0x00,0x10,0x1F,0x11,0x01,0x01,0x01,0x11,0x00,0x08,0xF8,0x08,0x00,0x00,0x00,0x08,

/* I */

0x00,0x10,0x1F,0x10,0x00,0x00,0x00,0x00,0x00,0x08,0xF8,0x08,0x00,0x00,0x00,0x00,

/* J */

0x00,0x00,0x10,0x1F,0x10,0x00,0x00,0x00,0x18,0x08,0x08,0xF0,0x00,0x00,0x00,0x00,

/* K */

0x00,0x10,0x1F,0x11,0x01,0x02,0x14,0x18,0x00,0x08,0xF8,0x08,0x80,0x40,0x28,0x18,

/* L */

0x00,0x10,0x1F,0x10,0x00,0x00,0x00,0x00,0x00,0x08,0xF8,0x08,0x08,0x08,0x08,0x18,

/* M */

0x00,0x10,0x1F,0x18,0x07,0x00,0x00,0x00,0x00,0x08,0xF8,0x08,0x00,0xE0,0x18,0xE0,

/* N */

0x00,0x10,0x1F,0x04,0x02,0x01,0x00,0x10,0x00,0x08,0xF8,0x08,0x00,0x80,0x40,0x20,

/* O */

0x00,0x07,0x08,0x10,0x10,0x10,0x10,0x10,0x00,0xE0,0x10,0x08,0x08,0x08,0x08,0x08,

/* P */

0x00,0x10,0x1F,0x10,0x10,0x10,0x10,0x0F,0x00,0x08,0xF8,0x88,0x80,0x80,0x80,0x00,

/* Q */

0x00,0x07,0x08,0x10,0x10,0x10,0x10,0x10,0x00,0xE0,0x10,0x08,0x08,0x0C,0x0A,0x0A,

/* R */

0x00,0x10,0x1F,0x11,0x11,0x11,0x11,0x0E,0x00,0x08,0xF8,0x08,0x00,0x80,0x60,0x18,

/* S */

0x00,0x0E,0x11,0x11,0x10,0x08,0x1C,0x00,0x00,0x38,0x10,0x08,0x88,0x88,0x70,0x00,

/* T */

0x18,0x10,0x10,0x10,0x1F,0x10,0x10,0x10,0x00,0x00,0x00,0x08,0xF8,0x08,0x00,0x00,

/* U */

0x00,0x10,0x1F,0x10,0x00,0x00,0x00,0x10,0x00,0x00,0xE0,0x10,0x08,0x08,0x08,0x10,

/* V */

0x10,0x10,0x1C,0x13,0x00,0x00,0x00,0x13,0x00,0x00,0x00,0x80,0x70,0x18,0x60,0x80,

/* W */

0x10,0x10,0x1E,0x11,0x00,0x10,0x13,0x1E,0x00,0x00,0x00,0xE0,0x18,0xE0,0x00,0x00,

/* X */

0x10,0x10,0x18,0x14,0x13,0x01,0x12,0x14,0x08,0x08,0x18,0x28,0x40,0x80,0x68,0x18,

/* Y */

0x00,0x10,0x10,0x1C,0x13,0x00,0x01,0x16,0x00,0x00,0x00,0x00,0x08,0xF8,0x08,0x00,

/* Z */

0x00,0x1C,0x10,0x10,0x11,0x16,0x18,0x10,0x08,0x18,0x68,0x88,0x08,0x08,0x08,0x18,

/* [ */

0x00,0x3F,0x20,0x20,0x00,0x00,0x00,0x00,0x00,0xFF,0x01,0x01,0x00,0x00,0x00,0x00,

/* \ */

0x30,0x0E,0x01,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0xE0,0x18,0x00,0x00,0x00,0x00,

/* ] */

0x20,0x20,0x3F,0x00,0x00,0x00,0x00,0x00,0x01,0x01,0xFF,0x00,0x00,0x00,0x00,0x00,

/* ^ */

0x03,0x0C,0x10,0x10,0x0C,0x03,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* _ */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x01,0x01,0x01,0x01,0x01,0x01,0x01,0x01,

/* ` */

0x00,0x10,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* a */

0x00,0x01,0x02,0x02,0x02,0x01,0x00,0x00,0x00,0x30,0x48,0x48,0x48,0xF8,0x08,0x00,

/* b */

0x10,0x3F,0x01,0x02,0x02,0x01,0x00,0x00,0x00,0xF0,0x08,0x08,0x08,0xF0,0x00,0x00,

/* c */

0x00,0x01,0x02,0x02,0x02,0x01,0x00,0x00,0x00,0xF0,0x08,0x08,0x08,0x10,0x00,0x00,

/* d */

0x00,0x01,0x02,0x02,0x11,0x3F,0x00,0x00,0x00,0xF0,0x08,0x08,0x10,0xF8,0x10,0x00,

/* e */

0x00,0x01,0x02,0x02,0x02,0x01,0x00,0x00,0x00,0xF0,0x88,0x88,0x88,0x90,0x00,0x00,

/* f */

0x00,0x02,0x1F,0x22,0x22,0x00,0x00,0x00,0x00,0x08,0xF8,0x08,0x08,0x00,0x00,0x00,

/* g */

0x00,0x01,0x02,0x02,0x02,0x03,0x02,0x00,0x00,0xD6,0x29,0x29,0x29,0xC9,0x06,0x00,

/* h */

0x10,0x3F,0x01,0x02,0x02,0x01,0x00,0x00,0x08,0xF8,0x08,0x00,0x08,0xF8,0x08,0x00,

/* i */

0x01,0x23,0x00,0x00,0x00,0x00,0x00,0x00,0x08,0xF8,0x08,0x00,0x00,0x00,0x00,0x00,

/* j */

0x01,0x23,0x00,0x00,0x00,0x00,0x00,0x00,0x01,0xFE,0x00,0x00,0x00,0x00,0x00,0x00,

/* k */

0x10,0x3F,0x00,0x00,0x03,0x02,0x02,0x00,0x08,0xF8,0x48,0xC0,0x28,0x18,0x08,0x00,

/* l */

0x10,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x08,0xF8,0x08,0x00,0x00,0x00,0x00,0x00,

/* m */

0x01,0x03,0x01,0x02,0x02,0x01,0x01,0x02,0x08,0xF8,0x08,0x00,0x08,0xF8,0x08,0x00,

/* n */

0x01,0x03,0x01,0x02,0x02,0x01,0x00,0x00,0x08,0xF8,0x08,0x00,0x08,0xF8,0x08,0x00,

/* o */

0x00,0x01,0x02,0x02,0x02,0x01,0x00,0x00,0x00,0xF0,0x08,0x08,0x08,0xF0,0x00,0x00,

/* p */

0x01,0x03,0x01,0x02,0x02,0x01,0x00,0x00,0x01,0xFF,0x11,0x08,0x08,0xF0,0x00,0x00,

/* q */

0x00,0x01,0x02,0x02,0x01,0x03,0x00,0x00,0x00,0xF0,0x08,0x08,0x11,0xFF,0x01,0x00,

/* r */

0x01,0x03,0x01,0x02,0x02,0x00,0x00,0x00,0x08,0xF8,0x08,0x00,0x00,0x00,0x00,0x00,

/* s */

0x00,0x01,0x02,0x02,0x03,0x00,0x00,0x00,0x00,0x98,0x48,0x48,0x30,0x00,0x00,0x00,

/* t */

0x02,0x0F,0x02,0x02,0x00,0x00,0x00,0x00,0x00,0xF8,0x08,0x10,0x00,0x00,0x00,0x00,

/* u */

0x02,0x03,0x00,0x00,0x02,0x03,0x00,0x00,0x00,0xF0,0x08,0x08,0x10,0xF8,0x10,0x00,

/* v */

0x02,0x03,0x02,0x00,0x02,0x03,0x02,0x00,0x00,0x80,0x70,0x08,0x70,0x80,0x00,0x00,

/* w */

0x02,0x03,0x02,0x00,0x02,0x03,0x02,0x00,0x00,0x80,0x70,0x18,0x60,0x80,0x70,0x18,

/* x */

0x02,0x03,0x02,0x00,0x02,0x03,0x02,0x00,0x08,0x18,0xA8,0x40,0xA8,0x18,0x08,0x00,

/* y */

0x02,0x03,0x02,0x00,0x02,0x03,0x02,0x00,0x01,0x81,0x62,0x1C,0x60,0x80,0x00,0x00,

/* z */

0x00,0x03,0x02,0x02,0x03,0x02,0x00,0x00,0x08,0x18,0x68,0x88,0x08,0x18,0x00,0x00,

/* { */

0x00,0x00,0x00,0x0F,0x10,0x20,0x00,0x00,0x00,0x00,0x80,0x7C,0x02,0x01,0x00,0x00,

/* | */

0x00,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,

/* } */

0x00,0x20,0x10,0x0F,0x00,0x00,0x00,0x00,0x00,0x01,0x02,0x7E,0x80,0x00,0x00,0x00,

/* ~ */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x40,0x80,0x80,0x80,0x40,0x40,0x40,0x80,

};

const unsigned char TimesNewRoman16[]=

{

/* */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* ! */

0x00,0x00,0x00,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0xFF,0xF0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x98,0x18,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* " */

0x00,0x00,0x07,0x07,0x00,0x00,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0xF0,0x80,0x00,0x00,0xF0,0x80,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* # */

0x00,0x00,0x00,0x01,0x0E,0x00,0x00,0x00,0x01,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,

0x21,0x21,0x27,0xF9,0x21,0x21,0x21,0x27,0xF9,0x21,0x21,0x00,0x00,0x00,0x00,0x00,

0x00,0x38,0xC0,0x00,0x00,0x00,0x38,0xC0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* $ */

0x00,0x01,0x03,0x06,0x04,0x0F,0x04,0x04,0x02,0x03,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0xE0,0xF0,0x38,0x18,0xFF,0x0C,0x06,0x03,0xC3,0x01,0x00,0x00,0x00,0x00,0x00,

0x00,0x70,0x18,0x08,0x08,0xFC,0x08,0x08,0x10,0xF0,0xE0,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* % */

0x00,0x01,0x03,0x06,0x04,0x06,0x03,0x01,0x00,0x00,0x00,0x00,0x00,0x01,0x02,0x04,

0x00,0xF0,0xF8,0x0C,0x04,0x0C,0xF8,0xF0,0x03,0x04,0x08,0x30,0x43,0x87,0x0C,0x08,

0x00,0x00,0x00,0x00,0x08,0x10,0x60,0x80,0x00,0x00,0x00,0x00,0xE0,0xF0,0x18,0x08,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* & */

0x00,0x00,0x00,0x00,0x00,0x01,0x03,0x06,0x04,0x04,0x06,0x03,0x00,0x00,0x00,0x00,

0x00,0x00,0x01,0x02,0x04,0xE8,0xF8,0x1E,0x17,0x23,0x41,0x80,0x11,0x1E,0x18,0x10,

0x00,0xE0,0xF0,0x18,0x08,0x08,0x08,0x08,0x10,0xA0,0xE0,0xF0,0x30,0x18,0x18,0x18,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* ' */

0x00,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0xF0,0x80,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* ( */

0x00,0x00,0x00,0x00,0x03,0x06,0x04,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x1F,0x7F,0xE0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0xC0,0xF8,0x1C,0x03,0x01,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x80,0x40,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* ) */

0x08,0x04,0x06,0x03,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0xE0,0x7F,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x01,0x03,0x1C,0xF8,0xE0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x40,0x80,0x80,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* * */

0x00,0x00,0x03,0x03,0x01,0x00,0x0F,0x00,0x01,0x03,0x03,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x30,0x30,0xE0,0xC0,0xFC,0xC0,0xE0,0x30,0x30,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* + */

0x00,0x00,0x00,0x00,0x00,0x00,0x03,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x08,0x08,0x08,0x08,0x08,0x08,0xFF,0x08,0x08,0x08,0x08,0x08,0x08,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0xE0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* , */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x18,0x18,0x19,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x80,0x80,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* - */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x03,0x03,0x03,0x03,0x03,0x03,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* . */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x18,0x18,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* / */

0x00,0x00,0x00,0x00,0x00,0x07,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x03,0x1C,0xE0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x08,0x70,0x80,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* 0 */

0x00,0x00,0x01,0x03,0x06,0x04,0x04,0x06,0x03,0x01,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x7F,0xFF,0x80,0x00,0x00,0x00,0x00,0x00,0xFF,0x7F,0x00,0x00,0x00,0x00,0x00,

0x00,0x80,0xE0,0x70,0x18,0x08,0x08,0x18,0x70,0xE0,0x80,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* 1 */

0x00,0x00,0x00,0x02,0x02,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* 2 */

0x00,0x00,0x03,0x06,0x06,0x06,0x06,0x07,0x03,0x01,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0xC0,0x00,0x00,0x00,0x00,0x03,0x06,0xF8,0xE0,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x08,0x18,0x38,0x58,0x98,0x18,0x18,0x18,0x38,0x20,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* 3 */

0x00,0x01,0x02,0x06,0x06,0x06,0x07,0x03,0x01,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x08,0x18,0x1C,0xEE,0xCF,0x03,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x18,0x18,0x08,0x08,0x08,0x08,0x10,0xE0,0xC0,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* 4 */

0x00,0x00,0x00,0x00,0x00,0x00,0x01,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x01,0x02,0x0C,0x30,0x40,0x80,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x80,0x80,0x80,0x80,0x80,0x80,0xF8,0xF8,0x80,0x80,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* 5 */

0x00,0x00,0x00,0x01,0x06,0x06,0x06,0x06,0x06,0x04,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x60,0xE0,0x60,0x70,0x30,0x38,0x1F,0x07,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x10,0x18,0x08,0x08,0x08,0x08,0x10,0x60,0x80,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* 6 */

0x00,0x00,0x00,0x00,0x01,0x01,0x02,0x02,0x04,0x04,0x04,0x00,0x00,0x00,0x00,0x00,

0x00,0x0F,0x3F,0xE8,0x90,0x10,0x10,0x18,0x1C,0x0F,0x07,0x00,0x00,0x00,0x00,0x00,

0x00,0x80,0xE0,0x30,0x18,0x08,0x08,0x08,0x10,0xE0,0xC0,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* 7 */

0x00,0x01,0x07,0x06,0x06,0x06,0x06,0x06,0x06,0x07,0x04,0x00,0x00,0x00,0x00,0x00,

0x00,0x80,0x00,0x00,0x00,0x00,0x03,0x1C,0xE0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x08,0x70,0x80,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* 8 */

0x00,0x01,0x03,0x06,0x04,0x04,0x04,0x04,0x06,0x03,0x01,0x00,0x00,0x00,0x00,0x00,

0x00,0xC0,0xE3,0x72,0x3C,0x1C,0x0C,0x1E,0x27,0xE3,0xC1,0x00,0x00,0x00,0x00,0x00,

0x00,0xE0,0xF0,0x18,0x08,0x08,0x08,0x08,0x18,0xF0,0xE0,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* 9 */

0x00,0x00,0x01,0x02,0x04,0x04,0x04,0x06,0x03,0x01,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0xF8,0xFC,0x0E,0x06,0x02,0x02,0x02,0x05,0xFF,0x7C,0x00,0x00,0x00,0x00,0x00,

0x00,0x08,0x08,0x08,0x10,0x10,0x20,0x60,0xC0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* : */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x30,0x30,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x18,0x18,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* ; */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x30,0x30,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x18,0x18,0x19,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x80,0x80,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* < */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x04,0x0A,0x0A,0x0A,0x11,0x11,0x20,0x20,0x20,0x40,0x40,0x40,0x80,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x80,0x80,0x80,0x40,0x40,0x40,0x20,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* = */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x22,0x22,0x22,0x22,0x22,0x22,0x22,0x22,0x22,0x22,0x22,0x22,0x22,0x22,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* > */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x80,0x40,0x40,0x40,0x20,0x20,0x20,0x11,0x11,0x0A,0x0A,0x0A,0x04,0x00,0x00,

0x00,0x20,0x40,0x40,0x40,0x80,0x80,0x80,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* ? */

0x00,0x01,0x02,0x04,0x04,0x04,0x06,0x03,0x01,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0xC0,0xC0,0x00,0x01,0x02,0x1C,0xF0,0xE0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0xD8,0x18,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* @ */

0x00,0x00,0x00,0x00,0x01,0x03,0x02,0x04,0x04,0x08,0x08,0x08,0x08,0x08,0x08,0x04,

0x00,0x0F,0x38,0xC0,0x80,0x00,0x01,0x07,0x1F,0x38,0x20,0x40,0x40,0x23,0x3F,0x7C,

0x00,0xF0,0x0C,0x03,0x01,0x00,0xF0,0xF8,0x08,0x08,0x10,0x20,0x78,0xF8,0x88,0x08,

0x00,0x00,0x00,0x00,0x80,0x80,0x40,0x40,0x20,0x20,0x20,0x20,0x20,0x20,0x40,0x40,

/* A */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x03,0x07,0x01,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x01,0x0F,0x31,0xC1,0x01,0x81,0xF1,0x7D,0x0F,0x03,0x00,0x00,0x00,

0x08,0x18,0x78,0x88,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x88,0xF8,0x78,0x18,0x08,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* B */

0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x04,0x04,0x04,0x06,0x03,0x03,0x01,0x00,0x00,

0x00,0x00,0x00,0xFF,0xFF,0x08,0x08,0x08,0x08,0x08,0x0C,0x1C,0xF6,0xE7,0x01,0x00,

0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x08,0x08,0x08,0x08,0x18,0x30,0xF0,0xC0,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* C */

0x00,0x00,0x00,0x01,0x03,0x02,0x04,0x04,0x04,0x04,0x04,0x06,0x02,0x03,0x07,0x00,

0x00,0x3F,0xFF,0xC0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x80,0xC0,0x00,

0x00,0x00,0xC0,0xE0,0x30,0x10,0x08,0x08,0x08,0x08,0x08,0x10,0x10,0x20,0x40,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* D */

0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x04,0x04,0x04,0x06,0x02,0x03,0x01,0x00,0x00,

0x00,0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0xC0,0xFF,0x3F,

0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x08,0x08,0x08,0x18,0x10,0x30,0xE0,0xC0,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* E */

0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x04,0x04,0x04,0x04,0x06,0x07,0x00,0x00,0x00,

0x00,0x00,0x00,0xFF,0xFF,0x08,0x08,0x08,0x08,0x08,0x3E,0x00,0x80,0x00,0x00,0x00,

0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x08,0x08,0x08,0x08,0x18,0x38,0x40,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* F */

0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x04,0x04,0x04,0x04,0x06,0x07,0x00,0x00,0x00,

0x00,0x00,0x00,0xFF,0xFF,0x08,0x08,0x08,0x08,0x3E,0x00,0x00,0x80,0x00,0x00,0x00,

0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* G */

0x00,0x00,0x00,0x01,0x03,0x02,0x04,0x04,0x04,0x04,0x04,0x06,0x02,0x03,0x07,0x00,

0x00,0x3F,0xFF,0xC0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x08,0x08,0x8F,0xCF,0x08,

0x00,0x00,0xC0,0xE0,0x30,0x10,0x18,0x08,0x08,0x08,0x08,0x08,0x18,0xF0,0xF0,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* H */

0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x00,0x00,0x00,0x04,0x04,0x07,0x07,0x04,0x04,

0x00,0x00,0x00,0xFF,0xFF,0x08,0x08,0x08,0x08,0x08,0x08,0x08,0xFF,0xFF,0x00,0x00,

0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x00,0x00,0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* I */

0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* J */

0x00,0x00,0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x30,0x38,0x18,0x08,0xF0,0xE0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* K */

0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x00,0x00,0x00,0x04,0x07,0x06,0x06,0x04,0x04,

0x00,0x00,0x00,0xFF,0xFF,0x0C,0x1E,0x17,0x23,0x41,0x80,0x00,0x00,0x00,0x00,0x00,

0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x00,0x80,0xC0,0xE8,0x78,0x38,0x18,0x18,0x08,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* L */

0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x08,0x08,0x08,0x08,0x18,0x78,0xE0,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* M */

0x00,0x04,0x04,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x03,

0x00,0x00,0x00,0xFF,0x80,0xE0,0xF8,0x3F,0x07,0x01,0x00,0x00,0x03,0x1C,0x60,0x80,

0x00,0x08,0x08,0xF8,0x08,0x08,0x00,0x00,0xC0,0xF0,0x78,0x60,0x80,0x00,0x08,0x08,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* N */

0x04,0x04,0x06,0x07,0x07,0x01,0x00,0x00,0x00,0x00,0x00,0x04,0x04,0x07,0x04,0x04,

0x00,0x00,0x00,0xFF,0x80,0xC0,0xF0,0x78,0x1C,0x0F,0x07,0x01,0x00,0xFF,0x00,0x00,

0x00,0x08,0x08,0xF8,0x08,0x08,0x00,0x00,0x00,0x00,0x80,0xC0,0xF0,0xF8,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* O */

0x00,0x00,0x00,0x01,0x03,0x02,0x04,0x04,0x04,0x04,0x04,0x02,0x03,0x01,0x00,0x00,

0x00,0x3F,0xFF,0xC0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0xC0,0xFF,0x3F,

0x00,0x00,0xC0,0xE0,0x30,0x10,0x08,0x08,0x08,0x08,0x08,0x10,0x30,0x60,0xC0,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* P */

0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x04,0x04,0x06,0x03,0x03,0x01,0x00,0x00,0x00,

0x00,0x00,0x00,0xFF,0xFF,0x04,0x04,0x04,0x04,0x0C,0x1C,0xF8,0xF0,0x00,0x00,0x00,

0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* Q */

0x00,0x00,0x00,0x01,0x03,0x02,0x04,0x04,0x04,0x04,0x04,0x02,0x03,0x01,0x00,0x00,

0x00,0x3F,0xFF,0xC0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0xC0,0xFF,0x3F,

0x00,0x00,0xC0,0xE0,0x30,0x18,0x0C,0x0C,0x0E,0x0F,0x0B,0x11,0x30,0x60,0xC0,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x80,0x80,0xC0,0x40,0x40,

/* R */

0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x04,0x04,0x06,0x07,0x03,0x01,0x00,0x00,0x00,

0x00,0x00,0x00,0xFF,0xFF,0x04,0x04,0x04,0x07,0x0F,0x19,0xF8,0xE0,0x00,0x00,0x00,

0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x00,0x00,0x80,0xE0,0x70,0x18,0x18,0x08,0x08,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* S */

0x00,0x01,0x03,0x06,0x04,0x04,0x04,0x02,0x03,0x07,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0xC0,0xF0,0x30,0x38,0x18,0x0C,0x0E,0x07,0xC3,0x01,0x00,0x00,0x00,0x00,0x00,

0x00,0xF8,0x30,0x10,0x08,0x08,0x08,0x08,0x18,0xF0,0xE0,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* T */

0x07,0x06,0x04,0x04,0x04,0x04,0x07,0x07,0x04,0x04,0x04,0x04,0x06,0x07,0x00,0x00,

0x80,0x00,0x00,0x00,0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x80,0x00,0x00,

0x00,0x00,0x00,0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* U */

0x04,0x04,0x07,0x07,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x04,0x04,0x07,0x04,0x04,

0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0xFF,0x00,0x00,

0x00,0x00,0xC0,0xF0,0x30,0x18,0x08,0x08,0x08,0x08,0x08,0x10,0x20,0xC0,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* V */

0x04,0x04,0x06,0x07,0x05,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x04,0x07,0x06,0x04,

0x00,0x00,0x00,0xC0,0xF8,0x3E,0x07,0x00,0x00,0x00,0x07,0x18,0x60,0x80,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0xC0,0xF8,0x38,0xC0,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* W */

0x04,0x04,0x06,0x07,0x07,0x04,0x00,0x00,0x04,0x04,0x07,0x07,0x04,0x04,0x00,0x00,

0x00,0x00,0x00,0xC0,0xF0,0x3E,0x07,0x01,0x00,0x01,0x0E,0xF8,0xFC,0x1F,0x03,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0xC0,0xF0,0x38,0xC0,0x00,0x00,0x00,0x80,0xE0,0x78,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* X */

0x00,0x04,0x04,0x06,0x07,0x07,0x04,0x04,0x00,0x00,0x00,0x04,0x04,0x07,0x06,0x04,

0x00,0x00,0x00,0x00,0x00,0xC0,0xE0,0x73,0x1C,0x0E,0x33,0x41,0x80,0x00,0x00,0x00,

0x00,0x08,0x08,0x18,0x38,0x68,0x80,0x00,0x00,0x00,0x88,0xC8,0x78,0x38,0x18,0x08,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* Y */

0x00,0x04,0x04,0x06,0x07,0x07,0x04,0x00,0x00,0x00,0x00,0x00,0x04,0x07,0x06,0x04,

0x00,0x00,0x00,0x00,0x80,0xC0,0xF0,0x38,0x0F,0x07,0x18,0x20,0xC0,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x08,0x08,0xF8,0xF8,0x08,0x08,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* Z */

0x00,0x07,0x06,0x04,0x04,0x04,0x04,0x04,0x04,0x05,0x07,0x06,0x04,0x00,0x00,0x00,

0x00,0x80,0x00,0x00,0x03,0x07,0x1C,0x38,0xF0,0xC0,0x80,0x00,0x00,0x00,0x00,0x00,

0x08,0x38,0x78,0xE8,0x88,0x08,0x08,0x08,0x08,0x08,0x08,0x08,0x38,0x60,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* [ */

0x00,0x00,0x0F,0x0F,0x08,0x08,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0xC0,0xC0,0x40,0x40,0x40,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* \ */

0x08,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0xE0,0x1C,0x03,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x80,0x70,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* ] */

0x00,0x08,0x08,0x08,0x0F,0x0F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0xFF,0xFF,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x40,0x40,0x40,0xC0,0xC0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* ^ */

0x00,0x00,0x00,0x03,0x04,0x04,0x03,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x08,0x30,0xC0,0x00,0x00,0x00,0x00,0xC0,0x30,0x08,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

/* _ */

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x40,0x40,0x40,0x40,0x40,0x40,0x40,0x40,0x40,0x40,0x40,0x40,0x00,0x00,0x00,0x00,

/* ` */

0x00,0x04,0x06,0x01,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x80,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,

0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,