. The linux kernel provides a complete 24 series EEPROM driver, which is located in the "kernel/drivers/misc" directory (at24.c), and can be used directly.

Compiling system: Ubuntu 16.04

ARM Hardware: firefly RK3399

ARM system: firstly Ubuntu 16.04 (SDK)

Connecting I2C: i2c4

EEPROM: AT24C02

1. EEPROM driving analysis

The 24 series EEPROM is based on the i2c interface, and chips from different manufacturers can be compatible with each other, such as atmel, st, microchip and some small brands. The source code provided by kernel is EEPROM (at24cxx) based on atmel.

1.1 private data

struct at24_data { struct at24_platform_data chip; /* Chip information */ struct memory_accessor macc; int use_smbus; /* If smbus is used */ int use_smbus_write; /* * Lock protects against activities from other Linux tasks, * but not from changes by other I2C masters. */ struct mutex lock; /* Read write mutex */ struct bin_attribute bin; /* Generate sys directory information after driver matching */ u8 *writebuf; /* Write buffer */ unsigned write_max; /* Write limit Max space */ unsigned num_addresses; /* * Some chips tie up multiple I2C addresses; dummy devices reserve * them for us, and we'll use them with SMBus calls. */ struct i2c_client *client[];/* i2c Bus, in the form of array, means that "multiple" i2c buses will be occupied, because 24 series EEPROM is 8-bit addressing when it is less than 16Mbit, and i2c is used to "turn page" addressing when it is more than 256 byte address*/ };

"at24 platform data" is declared in "kernel / include / Linux / platform data / at24. H".

struct at24_platform_data { u32 byte_len; /* size (sum of all addr) */ u16 page_size; /* for writes */ u8 flags; #define AT24_FLAG_ADDR16 0x80 /* address pointer is 16 bit */ #define AT24_FLAG_READONLY 0x40 /* sysfs-entry will be read-only */ #define AT24_FLAG_IRUGO 0x20 /* sysfs-entry will be world-readable */ #define AT24_FLAG_TAKE8ADDR 0x10 /* take always 8 addresses (24c00) */ void (*setup)(struct memory_accessor *, void *context); void *context; };

1.2 common model matching table

. When using the device tree description, the ". compatible" attribute must be consistent with the first attribute (device model).

static const struct i2c_device_id at24_ids[] = { /* needs 8 addresses as A0-A2 are ignored */ { "24c00", AT24_DEVICE_MAGIC(128 / 8, AT24_FLAG_TAKE8ADDR) }, /* old variants can't be handled with this generic entry! */ { "24c01", AT24_DEVICE_MAGIC(1024 / 8, 0) }, { "24c02", AT24_DEVICE_MAGIC(2048 / 8, 0) }, /* spd is a 24c02 in memory DIMMs */ { "spd", AT24_DEVICE_MAGIC(2048 / 8, AT24_FLAG_READONLY | AT24_FLAG_IRUGO) }, { "24c04", AT24_DEVICE_MAGIC(4096 / 8, 0) }, /* 24rf08 quirk is handled at i2c-core */ { "24c08", AT24_DEVICE_MAGIC(8192 / 8, 0) }, { "24c16", AT24_DEVICE_MAGIC(16384 / 8, 0) }, { "24c32", AT24_DEVICE_MAGIC(32768 / 8, AT24_FLAG_ADDR16) }, { "24c64", AT24_DEVICE_MAGIC(65536 / 8, AT24_FLAG_ADDR16) }, { "24c128", AT24_DEVICE_MAGIC(131072 / 8, AT24_FLAG_ADDR16) }, { "24c256", AT24_DEVICE_MAGIC(262144 / 8, AT24_FLAG_ADDR16) }, { "24c512", AT24_DEVICE_MAGIC(524288 / 8, AT24_FLAG_ADDR16) }, { "24c1024", AT24_DEVICE_MAGIC(1048576 / 8, AT24_FLAG_ADDR16) }, { "at24", 0 }, { /* END OF LIST */ } };

1.3 read function

static ssize_t at24_eeprom_read(struct at24_data *at24, char *buf, unsigned offset, size_t count) { struct i2c_msg msg[2]; /* i2c Bus message */ u8 msgbuf[2]; struct i2c_client *client; unsigned long timeout, read_time; int status, i; memset(msg, 0, sizeof(msg)); /* * REVISIT some multi-address chips don't rollover page reads to * the next slave address, so we may need to truncate the count. * Those chips might need another quirk flag. * * If the real hardware used four adjacent 24c02 chips and that * were misconfigured as one 24c08, that would be a similar effect: * one "eeprom" file not four, but larger reads would fail when * they crossed certain pages. */ /* * Slave address and byte offset derive from the offset. Always * set the byte address; on a multi-master board, another master * may have changed the chip's "current" address pointer. */ client = at24_translate_offset(at24, &offset);/* Get page turning offset address (bus) 0x50/0x51/0x52, etc */ if (count > io_limit) count = io_limit; if (at24->use_smbus) { /* Smaller eeproms can work given some SMBus extension calls */ if (count > I2C_SMBUS_BLOCK_MAX) count = I2C_SMBUS_BLOCK_MAX; } else { /* * When we have a better choice than SMBus calls, use a * combined I2C message. Write address; then read up to * io_limit data bytes. Note that read page rollover helps us * here (unlike writes). msgbuf is u8 and will cast to our * needs. */ i = 0; if (at24->chip.flags & AT24_FLAG_ADDR16) /* 16bit When addressing, transmit the high 8bit address first */ msgbuf[i++] = offset >> 8; msgbuf[i++] = offset; msg[0].addr = client->addr; msg[0].buf = msgbuf; msg[0].len = i; msg[1].addr = client->addr; /* i2c Slave address */ msg[1].flags = I2C_M_RD; /* Read mark */ msg[1].buf = buf; msg[1].len = count; } /* * Reads fail if the previous write didn't complete yet. We may * loop a few times until this one succeeds, waiting at least * long enough for one entire page write to work. */ timeout = jiffies + msecs_to_jiffies(write_timeout); do { read_time = jiffies; if (at24->use_smbus) { /* Using the smbus bus */ status = i2c_smbus_read_i2c_block_data_or_emulated(client, offset, count, buf); } else { status = i2c_transfer(client->adapter, msg, 2); /* Use i2c bus (default)*/ if (status == 2) status = count; } dev_dbg(&client->dev, "read %zu@%d --> %d (%ld)\n", count, offset, status, jiffies); if (status == count) return count; /* REVISIT: at HZ=100, this is sloooow */ msleep(1); } while (time_before(read_time, timeout)); /* Read timeout processing */ return -ETIMEDOUT; }

1.4 write function

static ssize_t at24_eeprom_write(struct at24_data *at24, const char *buf, unsigned offset, size_t count) { struct i2c_client *client; struct i2c_msg msg; /* i2c Bus message */ ssize_t status = 0; unsigned long timeout, write_time; unsigned next_page; if (offset + count > at24->chip.byte_len) return -EINVAL; /* Get corresponding I2C address and adjust offset */ client = at24_translate_offset(at24, &offset); /* Get page turning offset address (bus) 0x50/0x51/0x52, etc */ /* write_max is at most a page */ if (count > at24->write_max) /* Restricted scope */ count = at24->write_max; /* Never roll over backwards, to the start of this page */ next_page = roundup(offset + 1, at24->chip.page_size);/* Take integer next block address */ if (offset + count > next_page) /* Calculate non block address */ count = next_page - offset; /* If we'll use I2C calls for I/O, set up the message */ if (!at24->use_smbus) { int i = 0; msg.addr = client->addr; msg.flags = 0; /* Write logo */ /* msg.buf is u8 and casts will mask the values */ msg.buf = at24->writebuf; if (at24->chip.flags & AT24_FLAG_ADDR16) /* 16bit Address processing, transmitting high 8 bit address first */ msg.buf[i++] = offset >> 8; msg.buf[i++] = offset; memcpy(&msg.buf[i], buf, count); msg.len = i + count; } /* * Writes fail if the previous one didn't complete yet. We may * loop a few times until this one succeeds, waiting at least * long enough for one entire page write to work. */ timeout = jiffies + msecs_to_jiffies(write_timeout); do { write_time = jiffies; if (at24->use_smbus_write) { /* Using the sembus bus */ switch (at24->use_smbus_write) { case I2C_SMBUS_I2C_BLOCK_DATA: status = i2c_smbus_write_i2c_block_data(client, offset, count, buf); break; case I2C_SMBUS_BYTE_DATA: status = i2c_smbus_write_byte_data(client, offset, buf[0]); break; } if (status == 0) status = count; } else { /* Use i2c bus (default)*/ status = i2c_transfer(client->adapter, &msg, 1); if (status == 1) status = count; } dev_dbg(&client->dev, "write %zu@%d --> %zd (%ld)\n", count, offset, status, jiffies); if (status == count) return count; /* REVISIT: at HZ=100, this is sloooow */ msleep(1); } while (time_before(write_time, timeout));/* Write timeout processing */ return -ETIMEDOUT; }

1.5 matching function

static int at24_probe(struct i2c_client *client, const struct i2c_device_id *id) { struct at24_platform_data chip; kernel_ulong_t magic = 0; bool writable; int use_smbus = 0; int use_smbus_write = 0; struct at24_data *at24; int err; unsigned i, num_addresses; if (client->dev.platform_data) { /* If it exists, platform (device tree) is preferred to describe information */ chip = *(struct at24_platform_data *)client->dev.platform_data; } else { if (id) { magic = id->driver_data; /* Use at24? IDS description table */ } else { const struct acpi_device_id *aid; aid = acpi_match_device(at24_acpi_ids, &client->dev); /* acpi Table is less used in embedded system */ if (aid) magic = aid->driver_data; } if (!magic) return -ENODEV; chip.byte_len = BIT(magic & AT24_BITMASK(AT24_SIZE_BYTELEN)); magic >>= AT24_SIZE_BYTELEN; chip.flags = magic & AT24_BITMASK(AT24_SIZE_FLAGS); /* * This is slow, but we can't know all eeproms, so we better * play safe. Specifying custom eeprom-types via platform_data * is recommended anyhow. */ chip.page_size = 1; /* update chipdata if OF is present */ at24_get_ofdata(client, &chip); chip.setup = NULL; chip.context = NULL; } if (!is_power_of_2(chip.byte_len)) dev_warn(&client->dev, "byte_len looks suspicious (no power of 2)!\n"); if (!chip.page_size) { dev_err(&client->dev, "page_size must not be 0!\n"); return -EINVAL; } if (!is_power_of_2(chip.page_size)) dev_warn(&client->dev, "page_size looks suspicious (no power of 2)!\n"); ......... if (chip.flags & AT24_FLAG_TAKE8ADDR) /* Addressing type selection */ num_addresses = 8; else num_addresses = DIV_ROUND_UP(chip.byte_len, (chip.flags & AT24_FLAG_ADDR16) ? 65536 : 256); at24 = devm_kzalloc(&client->dev, sizeof(struct at24_data) + num_addresses * sizeof(struct i2c_client *), GFP_KERNEL); if (!at24) return -ENOMEM; mutex_init(&at24->lock); at24->use_smbus = use_smbus; at24->use_smbus_write = use_smbus_write; at24->chip = chip; at24->num_addresses = num_addresses; /* * Export the EEPROM bytes through sysfs, since that's convenient. * By default, only root should see the data (maybe passwords etc) */ sysfs_bin_attr_init(&at24->bin); /* Initialize build file directory information */ at24->bin.attr.name = "eeprom"; /* File name, matching succeeded, generated in "/ sys/bus/i2c/device/4-0050" directory */ at24->bin.attr.mode = chip.flags & AT24_FLAG_IRUGO ? S_IRUGO : S_IRUSR; at24->bin.read = at24_bin_read; at24->bin.size = chip.byte_len; at24->macc.read = at24_macc_read; writable = !(chip.flags & AT24_FLAG_READONLY); if (writable) { if (!use_smbus || use_smbus_write) { unsigned write_max = chip.page_size; at24->macc.write = at24_macc_write; at24->bin.write = at24_bin_write; at24->bin.attr.mode |= S_IWUSR; if (write_max > io_limit) write_max = io_limit; if (use_smbus && write_max > I2C_SMBUS_BLOCK_MAX) write_max = I2C_SMBUS_BLOCK_MAX; at24->write_max = write_max; /* buffer (data + address at the beginning) */ at24->writebuf = devm_kzalloc(&client->dev, write_max + 2, GFP_KERNEL); if (!at24->writebuf) return -ENOMEM; } else { dev_warn(&client->dev, "cannot write due to controller restrictions."); } } at24->client[0] = client; /* Use at least one i2c bus */ /* use dummy devices for multiple-address chips */ for (i = 1; i < num_addresses; i++) { /* When the address exceeds 256, an i2c bus (address) is assigned as the "page turning" function */ at24->client[i] = i2c_new_dummy(client->adapter, client->addr + i); if (!at24->client[i]) { dev_err(&client->dev, "address 0x%02x unavailable\n", client->addr + i); err = -EADDRINUSE; goto err_clients; } } err = sysfs_create_bin_file(&client->dev.kobj, &at24->bin); /* Create sys file, support echo/cat and other script access */ if (err) goto err_clients; i2c_set_clientdata(client, at24); dev_info(&client->dev, "%zu byte %s EEPROM, %s, %u bytes/write\n", at24->bin.size, client->name, writable ? "writable" : "read-only", at24->write_max); if (use_smbus == I2C_SMBUS_WORD_DATA || use_smbus == I2C_SMBUS_BYTE_DATA) { dev_notice(&client->dev, "Falling back to %s reads, " "performance will suffer\n", use_smbus == I2C_SMBUS_WORD_DATA ? "word" : "byte"); } /* export data to kernel code */ if (chip.setup) chip.setup(&at24->macc, chip.context); return 0; err_clients: for (i = 1; i < num_addresses; i++) if (at24->client[i]) i2c_unregister_device(at24->client[i]); return err; }

2. Use drive

2.1 add device tree

AT24C02 is connected to i2c4, and the i2c4 node in "kernel / arch / arm64 / boot / DTS / rockchip / rk3399-first-core.dtsi" is added to the EEPROM node.

eeprom: eeprom@50{ compatible = "24c02"; /* Consistent with drive description table */ reg = <0x50>; /* Device address */ status = "okay"; };

2.2 kernel configuration

Method [1]

.

Device Drivers ---> Misc devices ---> EEPROM support ---> <*> I2C EEPROMs / RAMs / ROMs from most vendors

Method [2]

.

. The second method is temporarily recommended.

CONFIG_EEPROM_AT24=y

2.3 compiling the kernel

execute ". / build.sh kernel" to compile the kernel under the sdk directory. The package file "boot.img" of kernel and device tree is generated in the "kernel" directory, and the kernel and device tree of replacement board are burned.

3. test

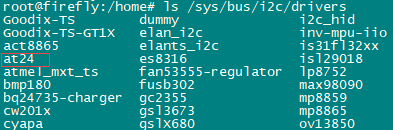

[1] View the driver and load it successfully. Generate the i2c driver name in the "/ sys/bus/i2c/drivers" directory

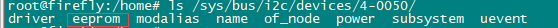

[2] View the sys file of the driver in "/ sys/busi2c/device/4-0050"

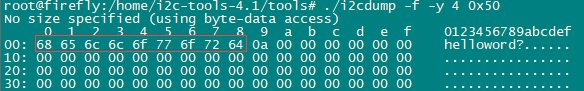

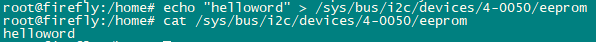

[3] Visit EEPROM

The sys file supports "echo", "cat" access.

You can also use the "i2ctools" tool to verify.