I. DUT

1.1 DUT port

Because the first LAB is relatively simple, here we first introduce DUT.

Relevant data SV_LAB, SV_TestbenchGuider and SV_LABGuider are EETOP search data.

Here is just to learn notes, convenient for their own viewing, write carelessly, hope to understand.

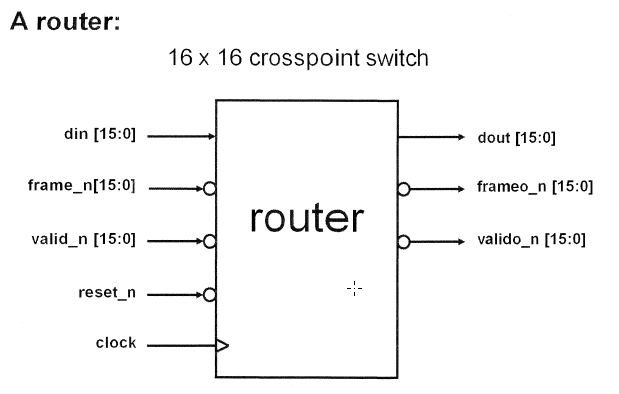

DUT is a router with 16 in and 16 out. You can see that din, frame_n and valid_n are all 16 bits. One DIN represents the input of a route. The same is true for dout.

1.2 DUT input timing

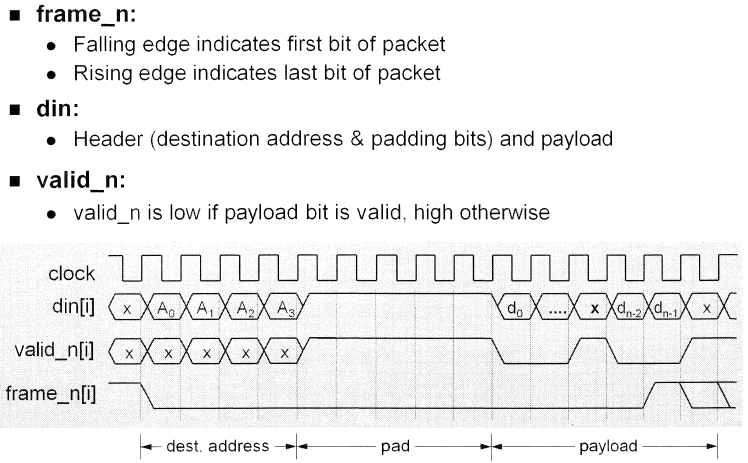

In the input sequence, start with frame_n pulling down and end with frame_n pulling up. Note that frame_n is high at the last data.

In the input sequence, din is divided into three parts: (1) addr accounts for four cycles, (2) pad accounts for five cycles, (3) data length is uncertain.

In the input sequence, valid_n does not pay attention to (1) input addr stage, is higher in (2) input pad stage, and indicates whether the data is valid in (3) input data stage.

The address is 4 bits, ranging from 0 to 15, indicating which dout the data should be forwarded from.

1.3 DUT Output Sequence

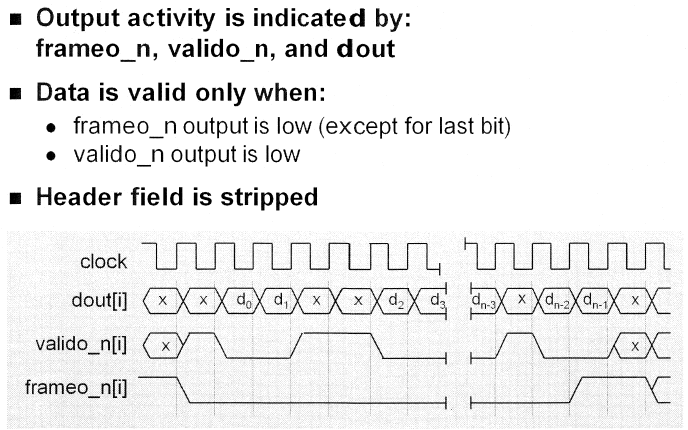

The output timing is relatively simple, using the frameo_n descending edge to indicate the beginning, and the frameo_n ascending edge to indicate the end.

Then, the forwarding sequence contains only the data phase, during which valid_n is used to indicate whether the data line is valid.

1.4 DUT Code Reference

Located in the rtl directory of sv_lab, the interface is the same as 1.1.

1.5 Interface code

Because of 6 lab s, the interface code router_io.sv is the same, so it is introduced in advance.

(1) Interface signal, defined by logic;

(2) clocking blocks are defined to define the clock domain and to specify the direction of the signal, where the direction is relative to the test platform.

(3) Use modport to group signals.

Here's what a big guy said. Let's put out a link. https://blog.csdn.net/liubin1222/article/details/81169314

An excerpt from a key point: "Perhaps this means: input 1ns means that the sampling time is 1 ns ahead of the rising edge of the clock, but it is not displayed on the waveform. It is used to simulate the setup time in real circuits. Output 1ns refers to the driving time being delayed by 1ns relative to the rising edge of the clock, which will be displayed on the waveform. It is used to simulate propagation delay in real circuits.

interface router_io(input bit clock); logic reset_n; logic [15:0] din; logic [15:0] frame_n; logic [15:0] valid_n; logic [15:0] dout; logic [15:0] valido_n; logic [15:0] busy_n; logic [15:0] frameo_n; clocking cb @(posedge clock); default input #1ns output #1ns; output reset_n; output din; output frame_n; output valid_n; input dout; input valido_n; input frameo_n; input busy_n; endclocking: cb modport TB(clocking cb, output reset_n); endinterface: router_io

II. Preliminary Test Platform of LAB1

2.1 Top router_trest_top.sv

(1) Define a signal, which is used as a clock.

bit SystemClock;

(2) A clock-driven interface variable is defined.

router_io top_io(SystemClock);

(3) Transfer the interface to a driver module

test t(top_io);

(4) Connect the interface to DUT

router dut(

.reset_n (top_io.reset_n),

.clock (top_io.clock),

.din (top_io.din),

.frame_n (top_io.frame_n),

.valid_n (top_io.valid_n),

.dout (top_io.dout),

.valido_n (top_io.valido_n),

.busy_n (top_io.busy_n),

.frameo_n (top_io.frameo_n)

);(5) Startup platform, mainly generated by the clock

initial begin

$timeformat(-9, 1, "ns", 10);

SystemClock = 0;

forever begin

#(simulation_cycle/2)

SystemClock = ~SystemClock;

end

end2.2 Driver code test.sv

(1) First, at the top level, variables of router_io type need to be passed in, and modport is specified, which should be to make sure whether the interface is input or output. (sv green paper is not around)

(2) In task reset() task, reset_n and other signals are set to default values, and then wait for 15 cycles to end the task.

program automatic test(router_io.TB rtr_io);

initial begin

$vcdpluson;

reset();

end

task reset();

rtr_io.reset_n = 1'b0;

rtr_io.cb.frame_n <= '1;

rtr_io.cb.valid_n <= '1;

##2 rtr_io.cb.reset_n <= 1'b1;

repeat(15) @(rtr_io.cb);

endtask: reset

endprogram: test