1. Cast type

1.1 static conversion (compile time conversion)

There are three types of static conversion, namely data type coercion, vector width coercion and symbol coercion. The formats are:

-

Data type cast: '()

7 + int'(2.0 * 3.0); //Converts the result of (2.0 * 3.0) to an integer //Then add 7

-

Vector width cast: '()

logic [15:0] a, b, y; y = a + b ** 16'(2); //Casts the text value 2 to 16 bits wide

-

Symbol cast: '()

shortint a, b; int y; y = y - singed'({a, b}); //Casts the splice result to a signed value

Static coercion is a compile time conversion. The conversion operation will always run without checking the validity of the results

The following simulates the data type cast and vector width cast:

module trans_static_tb;

int i;

logic [2:0] a;

initial begin

i = 1 + int'(1.0 + 2.0); //Static type conversion,

//Cast to int type

a = 3'b100;

end

initial begin

$display ("\n \t the var i is: %0d", i);

$display ("\n \t the array is: %b", 8'(a)); //Static type conversion,

//When printing, expand the width to 8 bits

end

endmodule

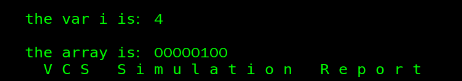

The simulation results are as follows:

1.2 dynamic cast

The system function $cast is dynamic and checks with converted values at run time

The format of dynamic cast is: $cast(dest_var, source_var);, The system function $cast has two variables: the target variable and the source variable

The following conditions can result in invalid cast:

-

Convert real type to int type, but the real number is too large to be described by int

int radius, area; always @(posedge clock) $cast (area, 3.154 * radius ** 2); //The result of the cast operator is replaced with an area type -

Converts a value to an enumeration type that is not in the list of legal values of the enumeration type

typedef enum {s1, s2, s3} state_t; state_t state, next_state; always_latch begin $cast (next_state, state + 1); end

$cast can be called as a task or a function. If the conversion fails when calling as a task, a runtime error will be reported, but when calling as a function, no runtime error will be reported

The system function $cast has a return value. If the conversion is successful, it returns 1; Conversion failed, return 0

For example:

typedef enum {s1, s2, s3} state_t;

state_t state, next_state;

always_comb begin

status = $cast(next_state, state + 1);

if(status == 0) //If the cast is not successful

next_state = s1;

end

The $cast function cannot be used with operators (+ +, + =) that directly modify the source expression

The main purpose of the $cast function is to assign the result of an expression to an enumeration type variable

Static coercion is integrable, while dynamic coercion may not support the $cast system function due to some integration tools

System functions and system tasks are not integrated

In the following example, replace 0.25 * 8 dynamic installation with int type, and judge whether the conversion is successful through the system function $cast

module trans_auto_tb;

bit a;

int value;

initial begin

a = $cast(value, 0.25 * 8); //Convert the value of 0.25 * 8 to type int

//If the conversion is successful, a is 1, otherwise a is 0

end

initial begin

$display ("\n \t a is: %b", a);

$display ("\n \t value is: %d", value);

end

endmodule

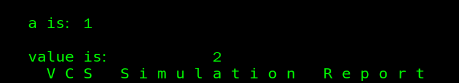

The simulation results are as follows:

2. Constant

2.1 constants in Verilog

Verilog provides three constant types: parameter, specparam, and localparam

- Parameter: a constant that can be redefined using defparam or inline parameter redefinition during establishment

- specparam: a constant that can be redefined from the SDF file at the time of establishment

- localparam: the establishment period constant cannot be redefined, but its value can be based on other constants

Establishment is essentially the process of software tools establishing the design level represented by module instances

Verilog restricts the declaration of parameter, specparam and localparam constants to modules, static tasks and static functions, but not to dynamic tasks and dynamic functions

2.2 constants in SV

The const keyword allows any variable to be declared as a constant. Constants in const form are not assigned until they are established

Use range of const constant:

- Declared in dynamic environments such as dynamic tasks and functions

- Given a network or variable value and a non constant expression

- Given an object value, this value can be defined at any design level

The declaration of const constant must contain a data type, for example:

const logic [23:0] C1 = 7; //24 bit constant const int C2 = 15; // 32-bit constant const real C3 = 3.14; // Real constant const C4 = 5; // Error because no data type was given

const constant is essentially a variable that can only be initialized